Estude fácil! Tem muito documento disponível na Docsity

Ganhe pontos ajudando outros esrudantes ou compre um plano Premium

Prepare-se para as provas

Estude fácil! Tem muito documento disponível na Docsity

Prepare-se para as provas com trabalhos de outros alunos como você, aqui na Docsity

Os melhores documentos à venda: Trabalhos de alunos formados

Prepare-se com as videoaulas e exercícios resolvidos criados a partir da grade da sua Universidade

Responda perguntas de provas passadas e avalie sua preparação.

Ganhe pontos para baixar

Ganhe pontos ajudando outros esrudantes ou compre um plano Premium

Comunidade

Peça ajuda à comunidade e tire suas dúvidas relacionadas ao estudo

Descubra as melhores universidades em seu país de acordo com os usuários da Docsity

Guias grátis

Baixe gratuitamente nossos guias de estudo, métodos para diminuir a ansiedade, dicas de TCC preparadas pelos professores da Docsity

Esquema eletrônico detalhado. Aplicação e teste.

Tipologia: Esquemas

1 / 70

Esta página não é visível na pré-visualização

Não perca as partes importantes!

**- Short Circuit Protection

- Direct Parallel Control of 16 channels for PWM

**- Low Quiescent Current

SCLK

SI

GND

VS

SO

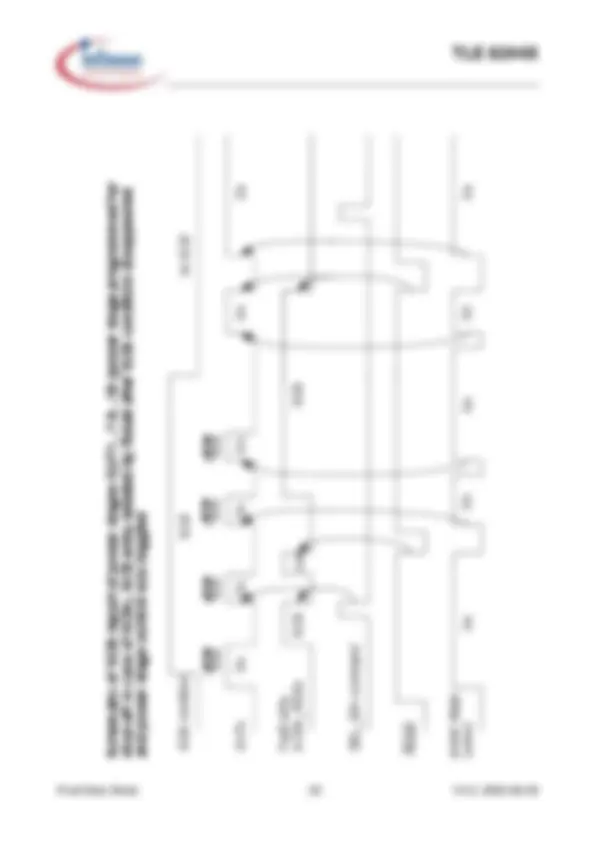

1 16

IN

OUT

OUT

V (^) BB

as Ch. 1

16

as Ch. 1 IN15 as Ch. 1 IN16 as Ch. 1

as Ch. 1 as Ch. 1

IN2 as Ch. 1

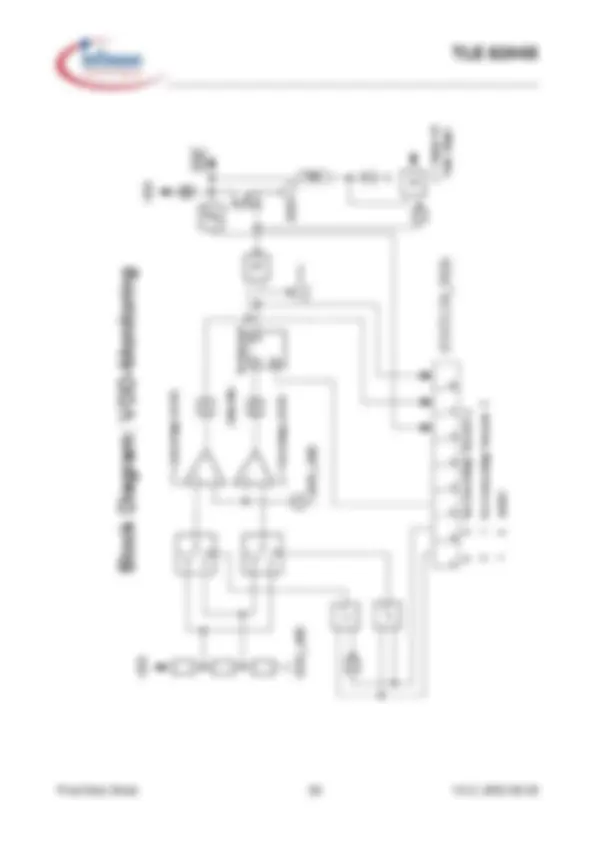

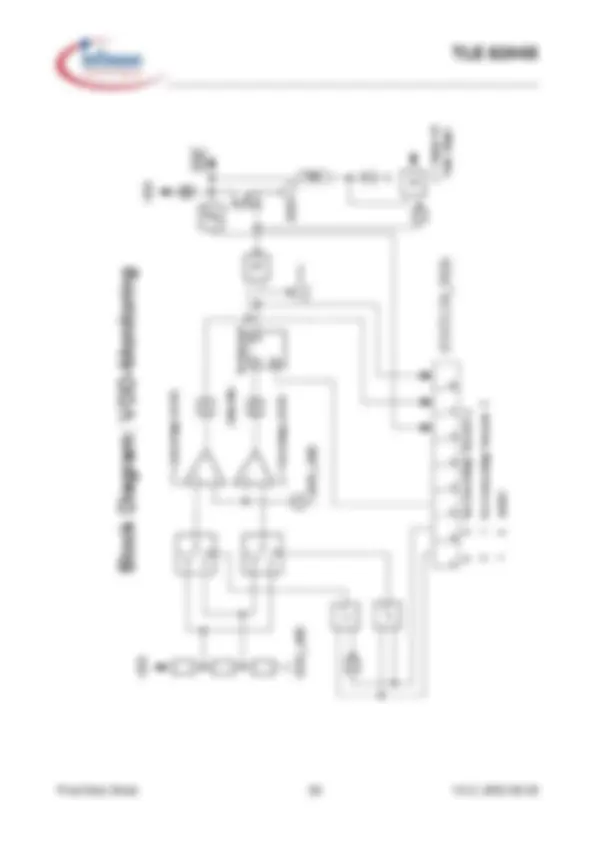

1. Description

1.1 Short Description

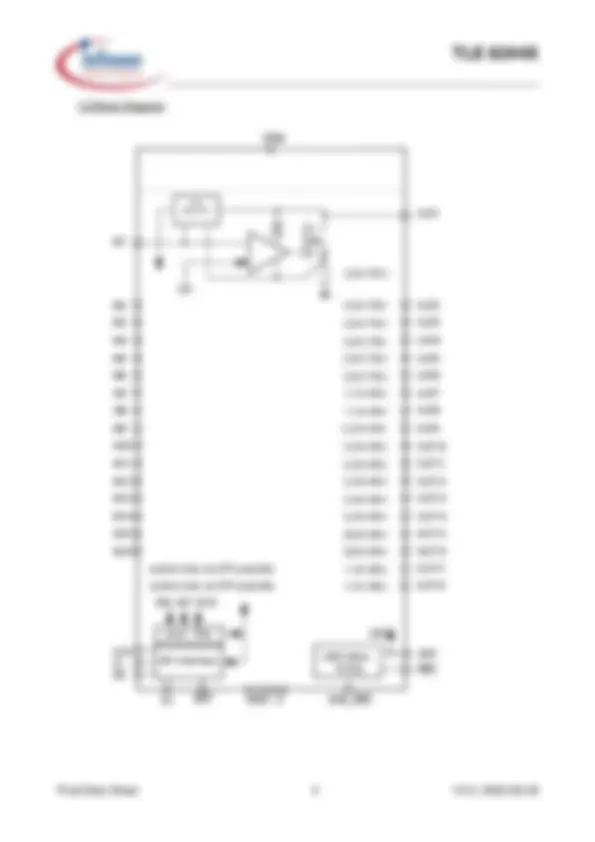

This circuit is available in MQFP64 package or as chip.

1.1.1 Features of the Power Stages

*) only serial control possible (via SPI)

Parallel connection of power stages is possible (see 1.13) Internal short-circuit protection Phase relation: non-inverting (exception: IN8->OUT8 is inverting)

1.1.2 Diagnostic Features

The following types of error can be detected: Short-circuit to UBatt (SCB) Short-circuit to ground (SCG) Open load (OL) Overtemperature (OT) Individual detection for each output. Serial transmission of the error code via SPI.

1.1.3 VDD-Monitoring

Low signal at pin ABE and shut-off of the power stages if VDD is out of the permitted range. Exception: If OUT8 is controlled by IN8, OUT8 will only be switched off by the overvoltage detection and not by undervoltage detection. The state of VDD can be read out via SPI.

1.1.4 μsec-bus Alternatively to the parallel and SPI control of the power stages, a high speed serial bus inter- face can be configured as control of the power stages OUT1...OUT7 and OUT9...OUT16.

1.1.5 Power Stage OUT OUT8 can be controlled by SPI or by the pin IN8 only. When controlled by IN8 this power stage

SPI mode the power stage is fully supervised by the VDD-monitor.

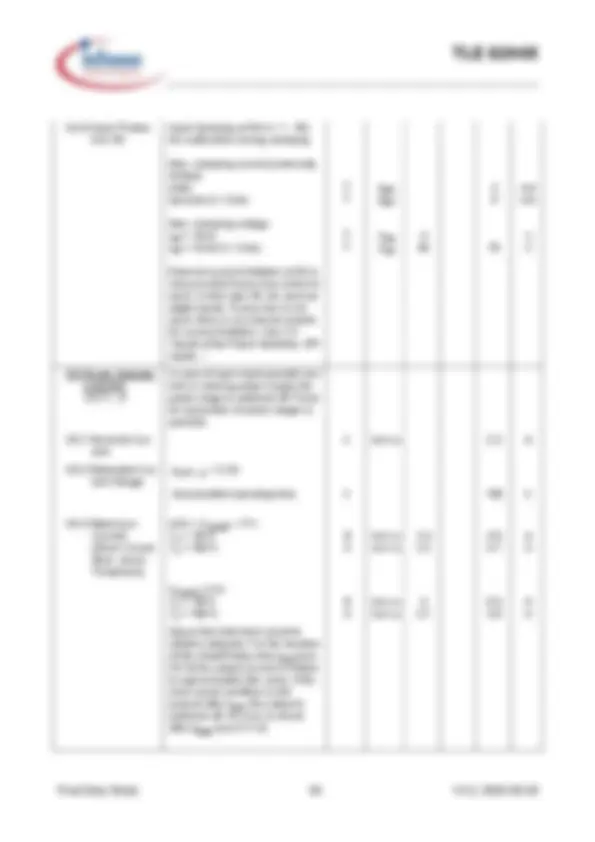

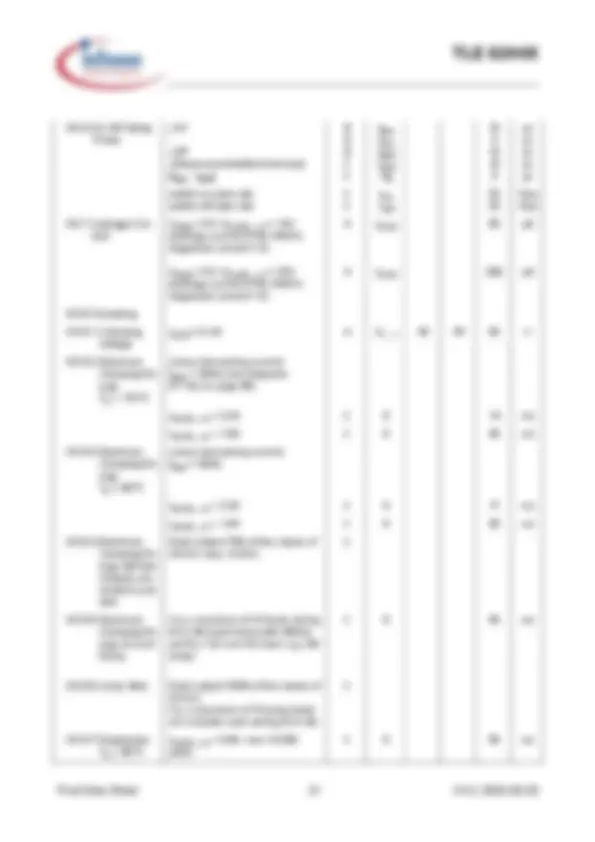

Nominal Current (^) R (^) on,max at T (^) J = 25°C static current limita- tion enabled by SPI

Clamping

OUT1, 2, 5, 6 2.2A^ 400mΩ^ -^ 70V

OUT3, OUT4 2.2A^ 380mΩ^ -^ 70V

OUT7, OUT8 1.1A^ 780mΩ^ -^ 45V

OUT9, OUT10 2.2A^ 380mΩ^ X^ 45V

OUT11...OUT14 2.2A^ 380mΩ^ -^ 45V

OUT15, OUT16 3.0A^ 280mΩ^ X^ 45V

*OUT17, OUT18 ) 1.1A^ 780mΩ^ X^ 45V

1.3 Description of the Power Stages

6 non-inverting low side power switches for nominal currents up to 2.2A. Control is possible by input pins, by the μsec-bus or via SPI. For T (^) J = 25°C the on-resistance of the power switches is below 400mΩ. An integrated zener diode limits the output voltage to 70V typically.

A protection for inverse current is implemented for OUT1... OUT4 for use as stepper-motor con- trol.

6 non-inverting low side power switches for nominal currents up to 2.2A. Control is possible by input pins, by the μsec-bus or via SPI. For T (^) J = 25°C the on-resistance of the power switches is below 380mΩ. An integrated zener diode limits the output voltage to 45V typically.

2 non-inverting low side power switches for nominal currents up to 3.0A. Control is possible by input pins, by the μsec-bus or via SPI. For T (^) J = 25°C the on-resistance of the power switches is below 280mΩ. An integrated zener diode limits the output voltage to 45V typically.

4 low side power switches for nominal currents up to 1100mA. Stage 7 is non-inverting, Stage 8 is inverting (IN8 = ‘1’ => OUT8 is active). For the output OUT7 control is possible by the input pin, by the μsec-bus or via SPI, OUT8 is controlled by the input pin IN8 or via SPI, for the outputs OUT17 and OUT18 control is only possible via SPI. For T (^) J = 25°C the on-resistance of the power switches is below 780mΩ. An integrated zener diode limits the output voltage to 45V typically.

In order to increase the switching current or to reduce the power dissipation parallel connection of power stages is possible (for additional information see 1.13). The power stages are short-circuit proof: Power stages OUT1...OUT8, OUT11.14 : In case of overload (SCB) they will be turned off after a given delay time. During this delay time the output current is limited by an internal current control loop. Power stages OUT9, OUT10, OUT15...OUT18 : In case of SCB these power stages can be configured for a shut-down mode or for static current limitation. In the shut down mode while SCB they will behave like OUT1..8 or OUT11..14. In case of static current limitation and SCB the current is limited and the corresponding bit com- bination is set (early warning) after a given delay time. They will not be turned off. If this condition leads to an overtemperature condition, the output will be set into a low duty cycle PWM (selective thermal shut- down with restart) to prevent critical chip temperature.

There are 3 possibilities to turn the power stages on again:

All low side switches are equipped with fault diagnostic functions:

The fault conditions SCB, SCG, OL and OT will not be stored until an integrated filtering time is expired (please note for PWM application). If, at one output, several errors occur in a sequence, always the last detected error will be stored (with filtering time). All fault conditions are encoded in two bits per switch and are stored in the corresponding SPI registers. Additionally there are two central diagnostic bits: one specially for OT and one for fault occurrence at any output.

The registers can be read out via SPI. After each read out cycle the registers have to be cleared by the DEL_DIA command.

1.3.1 Power Stage OUT8 (Condensed Description) 1.3.1.1 Control of OUT8 and VDD-Monitoring OUT8 can be controlled by SPI or by the pin IN8 only, control by μs-bus is not possible. When controlled by IN8 this power stage is functional if the voltage at the pin VDD is above 3,5V. In SPI mode the power stage is fully supervised by the VDD-monitor. If OUT8 is controlled by IN8, OUT8 will only be switched off by the overvoltage detection and not by undervoltage detection. 1.3.1.2 Phase Relation IN8 - OUT The phase relation IN8 -> OUT8 is inverting. OUT8 is active if IN8 is set to logic '1' (high level, see 3.4.2 ) in case of parallel access. On executing the read instruction on RD_INP1/2 the inverted status of IN8 is read back. 1.3.1.3 Reset / Power Stage Diagnostics If OUT8 is controlled by IN8, OUT8 will not be reseted by RST. After reset parallel control (by IN8) is active for OUT8. If UVDD < 4.5V errors are not stored because of the active RST of the external Regulator. Nev- ertheless OUT8 is protected against overload. 1.3.1.4 Input Current The control input IN8 has an internal pull-down current source. Thus the input currents I IN are positive (flow into the pin). 1.3.1.5 On Resistance For OUT8 and 3.5V < UVDD < 4.5V R on increases (see 3.8.5). 1.3.1.6 Parallel Connection of Power Stages Parallel connection of power stages with OUT8 and parallel control is prohibited (inverting input IN8). Control via SPI is possible. See 1.13.

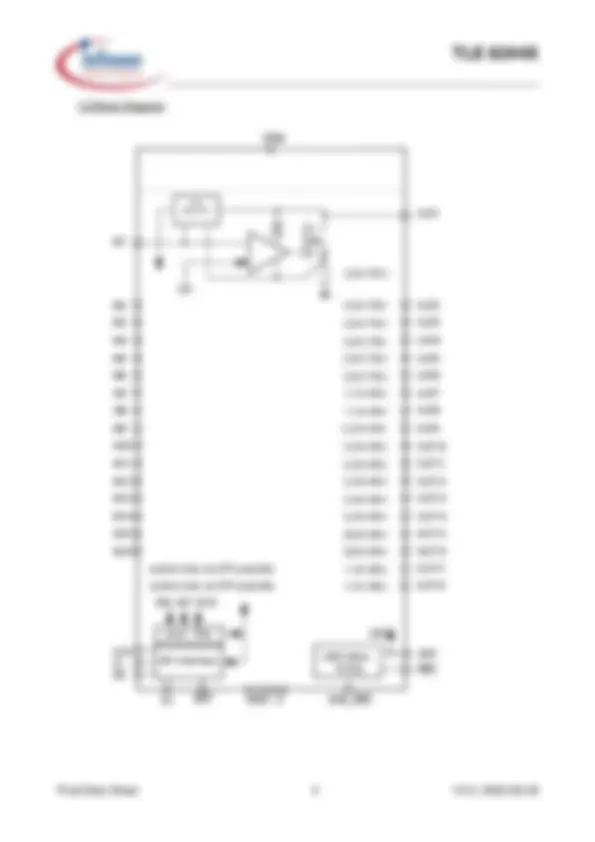

Supply Voltage VDD VDD 47 Supply Voltage U (^) Batt Ubatt 23

GND1 GND1 26 GND2 GND2 27 GND3 GND3 58 GND4 GND4 59 GND5 GND5 11 GND6 GND6 12 GND7 GND7 42 GND8 GND8 41

Sense Ground VDD-Monitoring GND_ABE 29 In-/Output VDD-Monitoring ABE 30 Reset (low active) RST 31

not connected nc 21, 24, 32, 52, 64

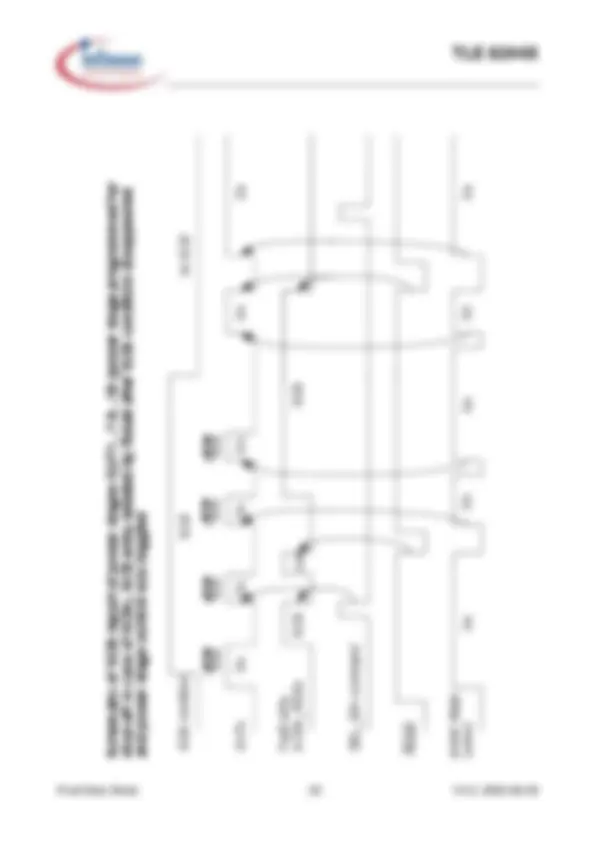

OUT6_

20

OUT5_

19

VDD

18

IN

17

OUT

16

OUT

15

14

GND

13

12 GND

OUT14_

11

OUT13_

10

OUT

9

8 OUT OUT

7

OUT

6

OUT10_

5

OUT9_

4

OUT6_

3

OUT5_

2

IN

1 52

IN

51

IN

50

OUT9_

49

OUT10_

48

GND

47

GND

46

IN

45

IN

44

OUT13_

43

OUT14_

42 41 40

IN

39

IN

38 37

OUT15_

36

OUT16_

35

IN

34

nc

33

nc

64

IN

63

Ubatt

62

n.c.

61

OUT

60

GND

59

GND

58

OUT

57 56 55 54 53

IN6 / FDA

21

IN16 / FCL

22

IN7 / SSY

23

OUT

24 25

GND

26 27 28 29 30 31 32

GND

OUT8SS SI SCK

GND_ABE

ABERST nc

nc SO

OUT15_

IN11 IN

OUT16_

IN

HiQUAD

1.5 Function of Pins

IN1 to IN16 Control inputs of the power stages

Internal pull-up current sources (exception: IN8 with pull-down current source)

FCL Clock for the μsec-bus (pin shared with IN16) FDA Data for the μsec-bus (pin shared with IN6) SSY Strobe and Synchronisation for the μsec-bus (pin shared with IN7)

OUT1 to OUT18 Outputs of the power switches

Short-circuit proof Low side switches Limitation of the output voltage by zener diodes

VDD Supply voltage 5V

UBatt Supply voltage U (^) Batt

Pin must not be left open but has to be connected either to U (^) Batt or to VDD (e.g. in commercial vehicles)

GND1 to GND8 Ground pins

Ground pins for the power stages (see 2.4) Ground reference of all logic signals is GND1/

RST Reset

Active low Locks all power switches regardless of their input signals (except OUT8) Clears the fault registers Resets the μsec-bus interface registers

ABE In-/Output VDD-Monitoring

Active low Output pin for the VDD-Monitoring Input pin for the shut-off signal coming from the supervisor

GND_ABE Sense ground VDD-Monitoring

SI, SO, SCK, SS SPI Interface

A SPI communication always starts with a SPI instruction sent from the controller to TLE6244X. During a write cycle the controller sends the data after the SPI instruction, beginning with the MSB. During a reading cycle, after having received the SPI instruction, TLE6244X sends the correspond- ing data to the controller, also starting with the MSB.

SPI Command/Format:

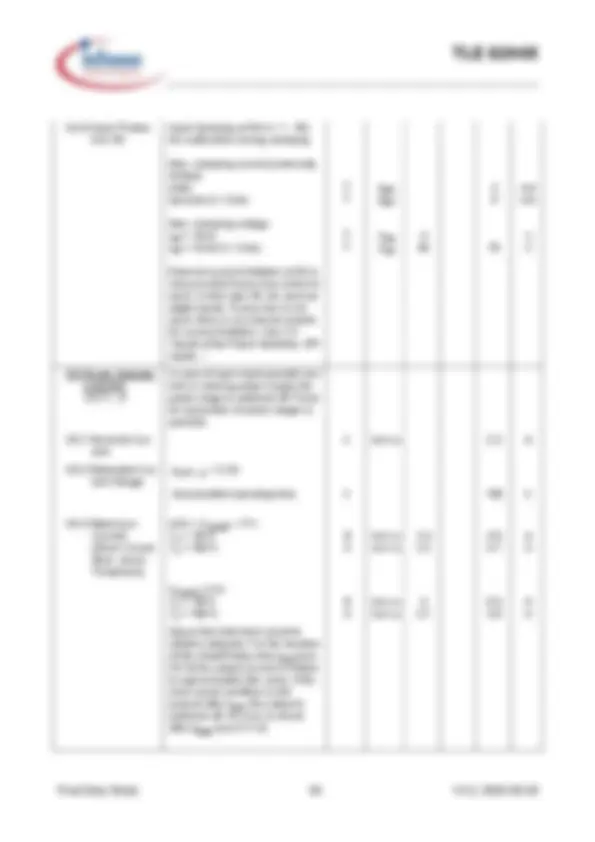

Characteristics of the SPI Interface:

If the slave select signal at SS is High, the SPI-logic is set on default condition, i.e. it expects an instruction.

If the 5V-reset (RST) is active, the SPI output SO is switched into tristate. The VDD monitoring (ABE) has no influence on the SPI interface.

Verification byte: Simultaneously to the receipt of an SPI instruction TLE6244X transmits a verification byte via the output SO to the controller. This byte indicates regular or irregular operation of the SPI. It contains an initial bit pattern and a flag indicating an invalid instruction of the previous access.

On a read access the databits at the SPI input SI are rejected. On a writing access or after the DEL_DIA instruction the TLE6244XTLE6244X sets the SPI output SO to low after sending the verification byte. If more than 16 bits are received the rest of the frame is rejected.

Invalid instruction/access: An instruction is invalid, if one of the following conditions is fulfilled:

After the bits CPAD1,0 and INSTR (4-0) have been sent from the microcontroller TLE6244X is able to check if the instruction code is valid. If an invalid instruction is detected, any modification on a register of TLE6244X is not allowed and the data byte ‘FFh’ is transmitted after having sent the verification byte. If a valid read instruction is detected the content of the corresponding register is transmitted to the controller after having sent the verification byte (even if bit INSW afterwards is wrong). If a valid write instruction is

7 6 5 4 3 2 1 0 0 0 INSTR4 INSTR3 INSTR2 INSTR1 INSTR0 INSW

Bit Name Description 7,6 CPAD1,0 Chip Address (has to be ‘0’, ‘0’) 5-1 INSTR (4-0) SPI instruction (encoding) 0 INSW Parity of the instruction

detected the data byte ’00h’ is transmitted to the controller after having sent the verification byte (even if bit INSW afterwards is wrong) but modifications on any register of TLE6244 are not allowed until bit INSW is valid, too.

If an invalid instruction is detected bit TRANS_F in the following verification byte is set to ’High’. This bit must not be cleared before it has been sent to the microcontroller.

SPI access format:

Verification byte:

MSB 7 6 5 4 3 2 1 0 Z Z 1 0 1 0 1 TRANS_F

Bit Name Description 0 TRANS_F Bit = 1: error detected during previous transfer Bit = 0: previous transfer was recognised as valid State after reset: 0 1 Fixed to High 2 Fixed to Low 3 Fixed to High 4 Fixed to Low 5 Fixed to High 6 send as high impedance 7 send as high impedance

MSB

SPI instruction

SS

SI

SO

MSB

Data 8bit

Check byte 00 00 00 00

MSB

SPI instruction XX XX XX XX

MSB

Data 8bit

READ-access (16bit) 8 bit command + 8bit data SS

SI

SO ZZ + 6bit

Check byte ZZ + 6bit Z=tristate

WRITE-access (16bit) 8 bit command + 8bit data

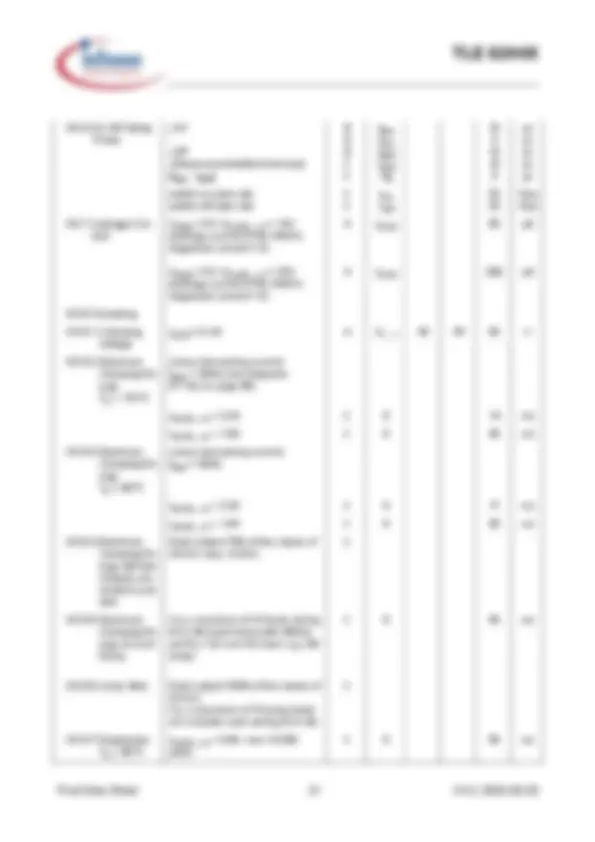

1.6.1 Serial/Parallel Control

Serial/Parallel Control of the Power Stages 1...16 and Serial Control (SPI) of the Power Stages 17 and 18: The registers MUX_REG1/2 and the bmux-bit prescribe parallel control or serial control (SPI or μsec- bus) of the power stages.

(SPI-Instructions: WR_MUX1...2, RD_MUX1...2, WR_SCON1...3, RD_SCON1...3)

The following table shows the truth table for the control of the power stages 1...18. The registers MUX_REG1, 2 prescribe parallel-control or serial control of the power stages. The registers SCON_REG1...3 prescribe the state of the power stage in case of SPI-serial control. BMUX deter- mines parallel control or control by μsec-bus. For the power stages 17 and 18 control is exclusively possible via SCON17/18. IN17/18 and MUX17/18 do not exist. BMUX has no function for OUT17/18.

Exception: OUT8 is on (active) if IN8 is set to logic ‘1’ (and off if IN8 is set to logic ‘0’) in case of parallel access.

Note: OUT8 cannot be controlled by the μsec-Bus. Refer to section 1.7.

ABE RST INx BMUX MUXx SCONx μsec- REGx

Output OUTx of Power Stage x, x = 1.. 0 0 X X X X X OUTx off 0 1 X X X X X OUTx off 1 0 X X X X X OUTx off 1 1 X X 0 0 X SPI Control: OUTx on 1 1 X X 0 1 X SPI Control: OUTx off 1 1 0 1 1 X X Parallel Control: OUTx on 1 1 1 1 1 X X Parallel Control: OUTx off 1 1 X 0 1 X 0 μsec-bus Control: OUTx on 1 1 X 0 1 X 1 μsec-bus Control: OUTx off

Description of the SPI Registers

Register: MUX_REG 7 6 5 4 3 2 1 0 MUX7 MUX6 MUX5 MUX4 MUX3 MUX2 MUX1 MUX

State of Reset: 80H Access by Controller: Read/Write Bit Name Description 0 MUX0 Serial or parallel control of power stage 1 1 MUX1 Serial or parallel control of power stage 2 2 MUX2 Serial or parallel control of power stage 3 3 MUX3 Serial or parallel control of power stage 4 4 MUX4 Serial or parallel control of power stage 5 5 MUX5 Serial or parallel control of power stage 6 6 MUX6 Serial or parallel control of power stage 7 7 MUX7 Serial or parallel control of power stage 8

Register: MUX_REG 7 6 5 4 3 2 1 0 MUX15 MUX14 MUX13 MUX12 MUX11 MUX10 MUX9 MUX

State of Reset: 00H Access by Controller: Read/Write Bit Name Description 0 MUX8 Serial or parallel control of power stage 9 1 MUX9 Serial or parallel control of power stage 10 2 MUX10 Serial or parallel control of power stage 11 3 MUX11 Serial or parallel control of power stage 12 4 MUX12 Serial or parallel control of power stage 13 5 MUX13 Serial or parallel control of power stage 14 6 MUX14 Serial or parallel control of power stage 15 7 MUX15 Serial or parallel control of power stage 16

Register: SCON_REG

7 6 5 4 3 2 1 0 1 1 1 1 1 1 SCON17 SCON

State of Reset: FFH Access by Controller: Read/Write Bit Name Description 0 SCON16 State of serial control of power stage 17 1 SCON17 State of serial control of power stage 18 7-2 No function: HIGH on reading

1.6.2 Diagnostics/Encoding of Failures

Description of the SPI Registers

(SPI Instructions: RD_DIA1...5)

Register: DIA_REG 7 6 5 4 3 2 1 0 DIA7 DIA6 DIA5 DIA4 DIA3 DIA2 DIA1 DIA

State of Reset: FFH Access by Controller: Read only Bit Name Description 1-0 DIA (1-0) Diagnostic Bits of power stage 1 3-2 DIA (3-2) Diagnostic Bits of power stage 2 5-4 DIA (5-4) Diagnostic Bits of power stage 3 7-6 DIA (7-6) Diagnostic Bits of power stage 4

Register: DIA_REG 7 6 5 4 3 2 1 0 DIA15 DIA14 DIA13 DIA12 DIA11 DIA10 DIA9 DIA

State of Reset: FFH Access by Controller: Read only Bit Name Description 1-0 DIA (9-8) Diagnostic Bits of power stage 5 3-2 DIA (11-10) Diagnostic Bits of power stage 6 5-4 DIA (13-12) Diagnostic Bits of power stage 7 7-6 DIA (15-14) Diagnostic Bits of power stage 8

Register: DIA_REG

7 6 5 4 3 2 1 0 1 1 1 UBatt DIA35 DIA34 DIA33 DIA

State of Reset: FFH Access by Controller: Read only Bit Name Description 1-0 DIA (33-32) Diagnostic Bits of power stage 17 3-2 DIA (35-34) Diagnostic Bits of power stage 18 4 UBatt 0: Voltage Level at Pin UBatt is below 2V (typically) 1: Voltage Level at Pin UBatt is above 2V (typically) Diagnosis of UBatt is only possible if UVDD > 4.5V Status of UBatt is not latched. 7-5 No function: High on reading

Encoding of the Diagnostic Bits of the Power Stages DIA(2x-1) DIA(2x-2) State of power stage x x = 1.. 1 1 Power stage o.k. 1 0 Short-circuit to U (^) Batt (SCB) / OT 0 1 Open load (OL) 0 0 Short-circuit to ground (SCG)

1.6.3 Configuration

The μsec-bus is enabled by this register. In addition the shut off at SCB can be configured for the power-stages OUT9, OUT10 and OUT15... OUT18.

Description of the μsec-bus see chapter 1.

CONFIG (Read and write) 7 6 5 4 3 2 1 0 O16-SCB O15-SCB O10-SCB O9-SCB O18-SCB O17-SCB BMUX 1

State of Reset: FFh Bit Name Description 0 No function: HIGH on reading 1 BMUX 1: parallel inputs INx enabled 0: μsec-Bus Interface enabled 2 O17-SCB 1: The output OUT17 is switched off in case of SCB 0: The output is not switched off in case of SCB 3 O18-SCB 1: The output OUT18 is switched off in case of SCB 0: The output is not switched off in case of SCB 4 O9-SCB 1: The output OUT9 is switched off in case of SCB 0: The output is not switched off in case of SCB 5 O10-SCB 1: The output OUT10 is switched off in case of SCB 0: The output is not switched off in case of SCB 6 O15-SCB 1: The output OUT15 is switched off in case of SCB 0: The output is not switched off in case of SCB 7 O16-SCB 1: The output OUT16 s switched off in case of SCB 0: The output is not switched off in case of SCB