Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

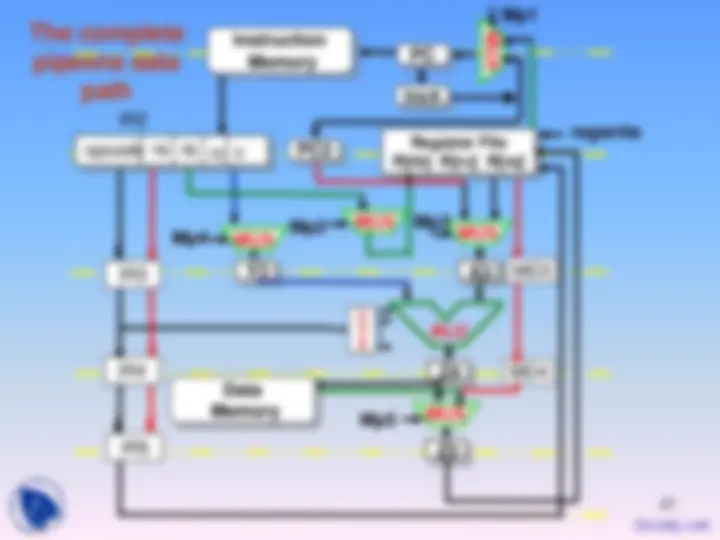

SRC Pipelined Hardware Block Diagram, Stages, Registers, ALU operation, Memory access, Control signals, Instruction decode are the topics professor discussed in this class.

Typology: Slides

1 / 23

This page cannot be seen from the preview

Don't miss anything!

1

Instruction Fetch

Decode and Operand Read

Operation

Memory Access

Register Writeback

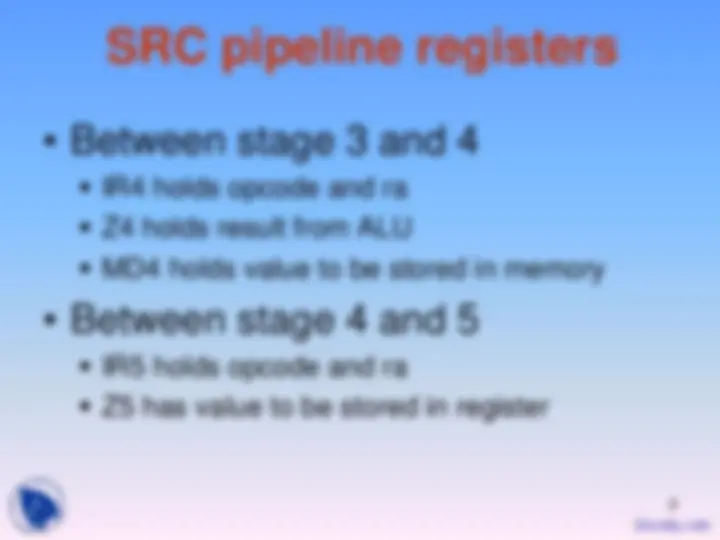

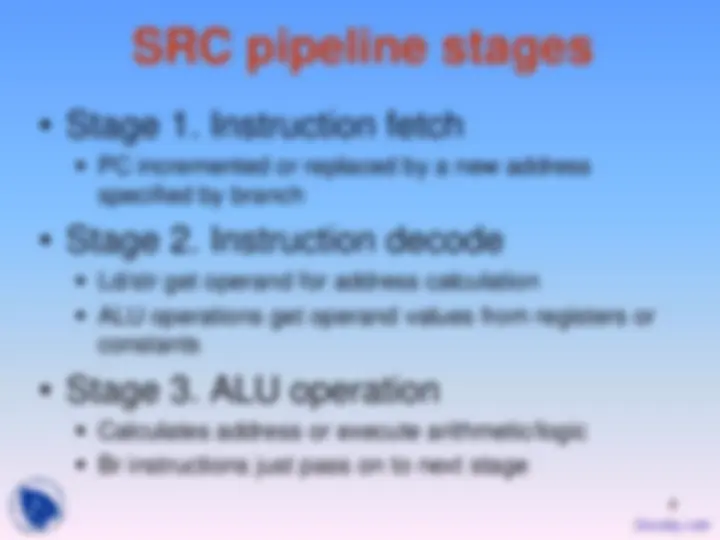

Pipeline Registers

Pipeline Stages

2

4

PC incremented or replaced by a new address specified by branch

Ld/str get operand for address calculation

ALU operations get operand values from registers or constants

Calculates address or execute arithmetic/logic

Br instructions just pass on to next stage

5

7

Instruction Fetch

Decode and Operand Read

Operation

Memory Access

Register Writeback

Instruction Memory PC Inc

Register File R[rb] R[rc] R[ra]

Mp4^ MUX

decoder

Op code •••^ regwrite ra c

X3 and Y3 are temporary reg to hold the values between pipeline stages

ALU Instruction

8

Instruction Fetch

Decode and Operand Read

Operation

Memory Access

Register Writeback

Instruction Memory PC Inc

Register File R[rb] R[rc] R[ra]

Mp4^ MUX

decoder

Op code •••^ regwrite ra c

X3 and Y3 are temporary reg to hold the values between pipeline stages

ALU computes the result

ALU Instruction

10

Instruction Fetch

Decode and Operand Read

Operation

Memory Access

Register Writeback

Instruction Memory PC Inc

Register File R[rb] R[rc] R[ra]

Mp4^ MUX

decoder

Op code •••^ regwrite ra c

X3 and Y3 are temporary reg to hold the values between pipeline stages

ALU computes the result

Result stored In destination

ALU Instruction

No memory access for ALU inst.

11

Instruction Fetch

Decode and Operand Read

Operation

Memory Access

Register Writeback

Instruction Memory PC Inc

Register File R[rb] R[rc] R[ra]

Mp3^ MUX

decoder

Op codera c1 PC2^ regwrite

Mp4^ MUX

Mp5 MUX

Data Memory

add

Load/Store

Instruction

13

Instruction Fetch

Decode and Operand Read

Operation

Memory Access

Register Writeback

Instruction Memory PC Inc

Register File R[rb] R[rc] R[ra]

Mp3^ MUX

decoder

Op codera c1 PC2^ regwrite

Mp4^ MUX

Mp5 MUX

Data Memory

add

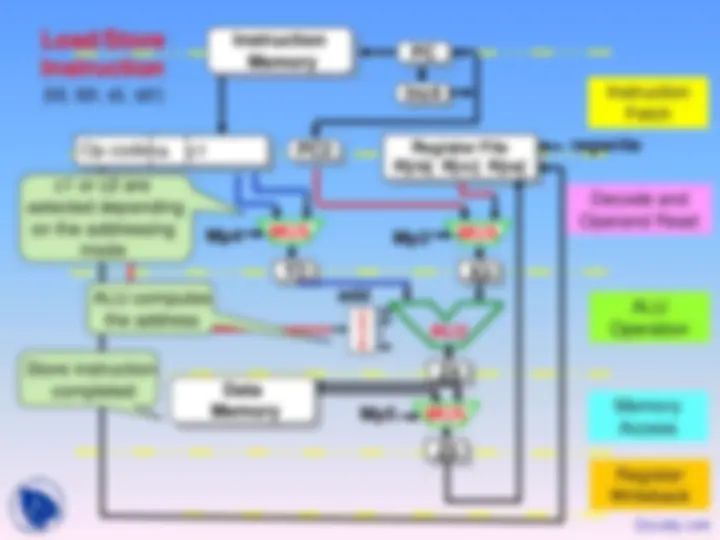

Load/Store Instruction

c1 or c2 are selected depending on the addressing mode

c1 or c2 are selected depending on the addressing mode

ALU computes the address

ALU computes the address

14

Instruction Fetch

Decode and Operand Read

Operation

Memory Access

Register Writeback

Instruction Memory PC Inc

Register File R[rb] R[rc] R[ra]

Mp3^ MUX

decoder

Op codera c1 PC2^ regwrite

Mp4^ MUX

Mp5 MUX

Data Memory

add

Load/Store Instruction

c1 or c2 are selected depending on the addressing mode

c1 or c2 are selected depending on the addressing mode

ALU computes the address

ALU computes the address

Store instruction completed

16

Instruction Fetch

Decode and Operand Read

Operation

Memory Access

Register Writeback

Instruction Memory PC Inc

Register File R[rb] R[rc] R[ra]

Op code ra ••• (^) c2^ regwrite

Branch Logic

condition

Branch Instruction

17

Instruction Fetch

Decode and Operand Read

Operation

Memory Access

Register Writeback

Instruction Memory PC Inc

Register File R[rb] R[rc] R[ra]

Op code ra ••• (^) c2^ regwrite

Branch Logic

condition

Branch Instruction

PC incremented as usual

19

Instruction Fetch

Decode and Operand Read

Operation

Memory Access

Register Writeback

Instruction Memory PC Inc

Register File R[rb] R[rc] R[ra]

Op code ra ••• (^) c2^ regwrite

Branch Logic

condition

Branch Instruction

PC incremented as usual

No memory access

Condition decides new PC value

20

Instruction Fetch

Decode and Operand Read

Operation

Memory Access

Register Writeback

Instruction Memory

Register File R[rb] R[rc] R[ra]

Op code ra ••• (^) c2^ regwrite

Branch Logic

condition

Inc

Branch Instruction

PC incremented as usual

No memory access

Only brl instructions write register

Condition decides new PC value