Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

SPARC Registers, General purpose registers, Processor Status Register, Program Counters, Register Windows, Memory Organization, Addressing modes are the topics professor discussed in this class.

Typology: Slides

1 / 36

This page cannot be seen from the preview

Don't miss anything!

1

2

Integer Registers

r

r

31 0

Floating Point Registers

r

r

31 0 nPC

(^31 )

(^31 )

(^31 )

(^31 )

(^31 )

(^31 )

PC

IR

Y

TBR

WIM

Multiply Step Register Trap base Register

Window Invalid mask

4

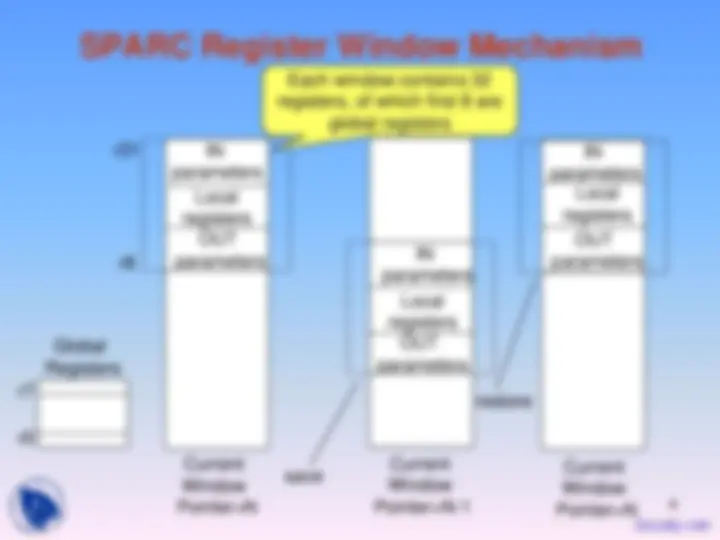

SPARC Register Window Mechanism

IN parameters Local registers OUT parameters

IN parameters Local registers OUT parameters

Current Window Pointer=N-

Current Window Pointer=N

save

restore

IN parameters

OUT parameters

Local registers

Current Window Pointer=N

r

r

Each window contains 32 registers, of which first 8 are global registers

r

r

Global Registers

5

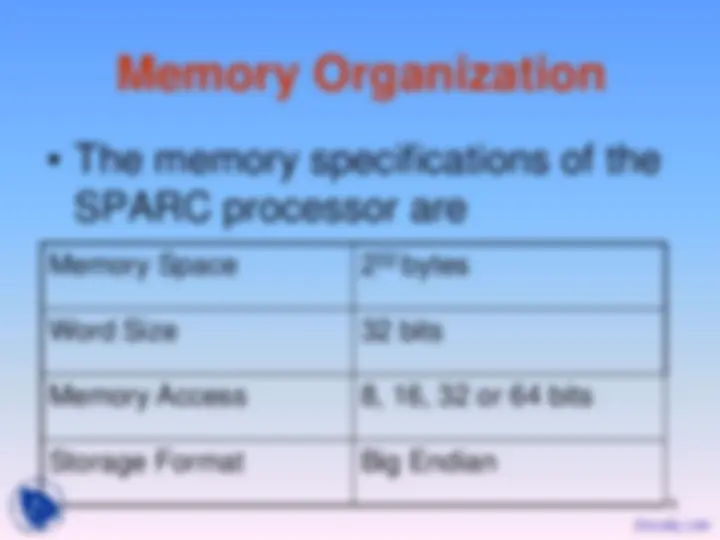

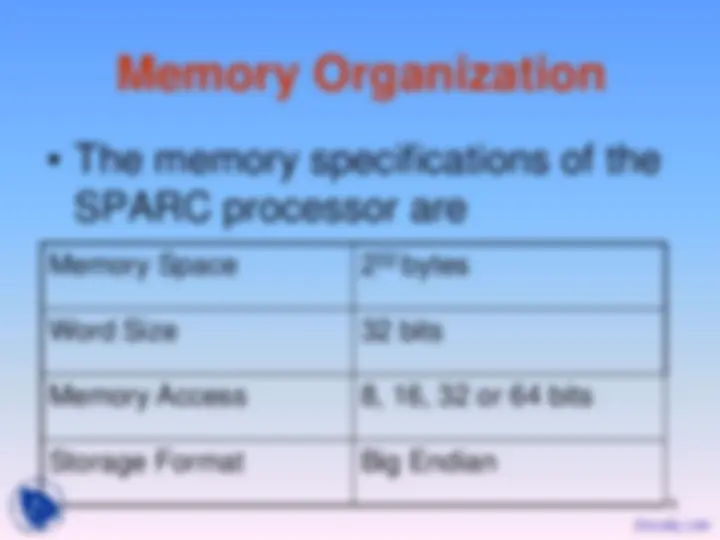

SPARC processor are

7

SPARC Instruction formats

31 0 op displacement

29

(^310) op a cond op2 disp

(^2928 2524 22 )

op (^) rd op2 disp

(^310) op op3 rs1 rs

29 25 24 19 opf

(^18141354)

op (^) rd op3 (^) rs1 0 asi op (^) rd op3 (^) rs1 (^1) simm

rs

rd

8

10

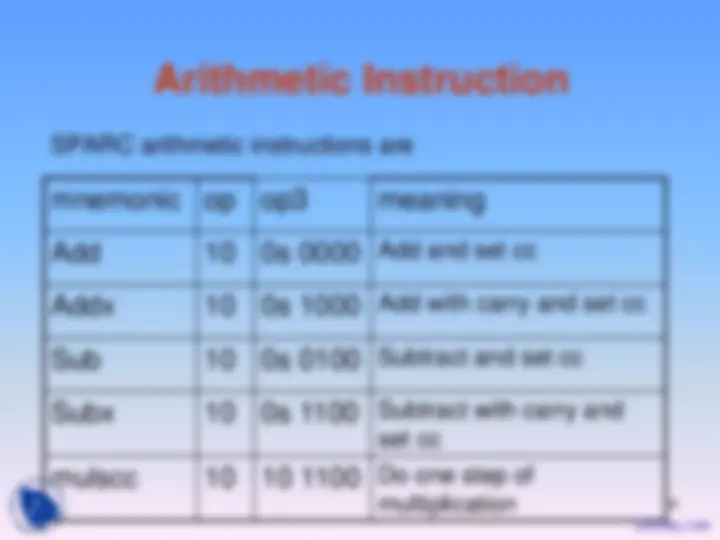

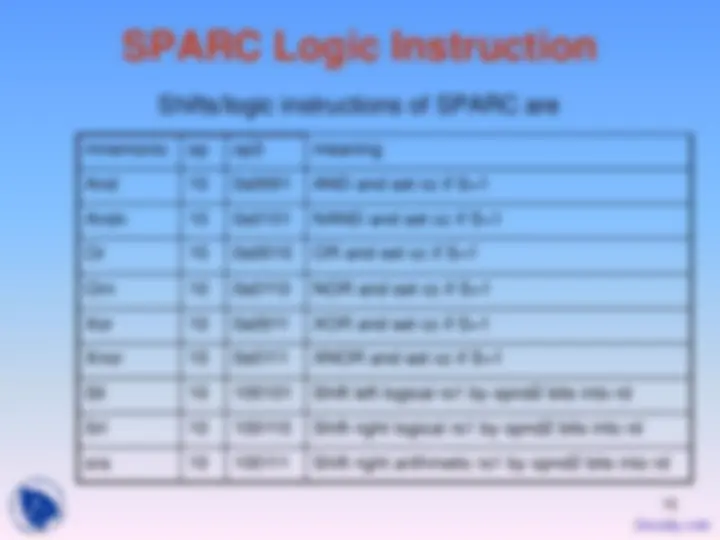

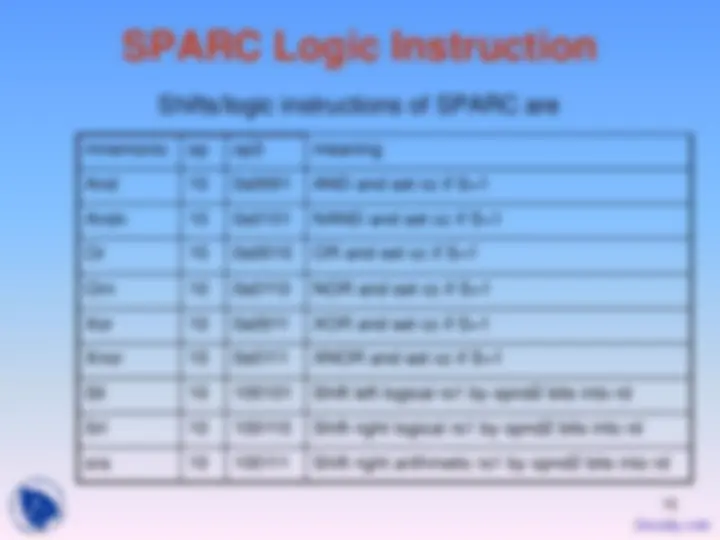

SPARC Logic Instruction

mnemonic op op3 meaning

And 10 0s0001 AND and set cc if S=

Andn 10 0s0101 NAND and set cc if S=

Or 10 0s0010 OR and set cc if S=

Orn 10 0s0110 NOR and set cc if S=

Xor 10 0s0011 XOR and set cc if S=

Xnor 10 0s0111 XNOR and set cc if S=

Sll 10 100101 Shift left logical rs1 by opnd2 bits into rd

Srl 10 100110 Shift right logical rs1 by opnd2 bits into rd

sra 10 100111 Shift right arithmetic rs1 by opnd2 bits into rd

11

13

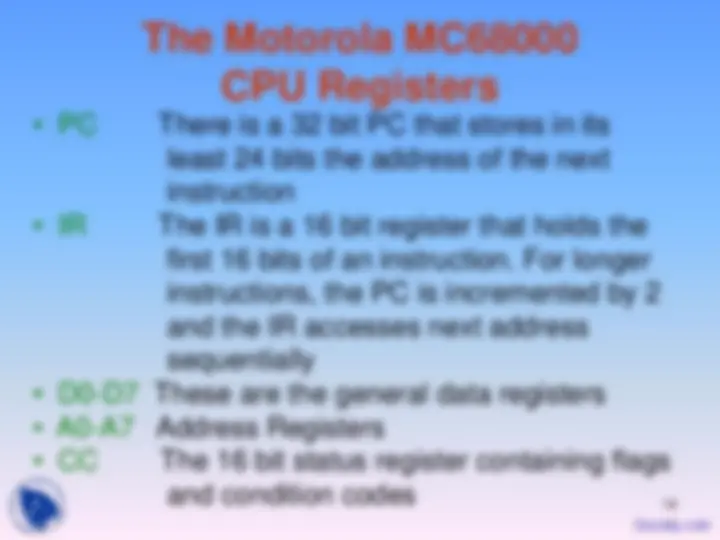

The Motorola MC

14

The Motorola MC

CPU Registers

16

Mc68000 are

17

MC68000 addressing modes

Addressing mode Notation Operand Location

Data register direct Dn Dn

Address register direct An An

Address register indirect (An) Mem[An]

Autoincrement (An)+ Mem[An];An ← An+WS

Autodecrement -(An) An←An-WS;Mem[An]

Based Disp16(An) Mem[An+disp16]

Based indexed short Disp8(An,Xnlo) mem{[An+Xnlo+disp8]

Based indexed long Disp8(An,Xn) Mem[An+Xn+disp8]

Absolute short Addr16 Mem[addr16]

Absolute long Addr32 Mem[addr32]

Relative Disp16(PC) Mem[PC+disp16]

Relative indexed short Disp8(PC,xnlo) Mem[PC+Xnlo+disp8]

Relative indexed long Disp8(PC,Xn) Mem[PC+Xn+disp8]

Immediate #data nil

Low order 16 bits of any data or address register

Any of D0-D7 or A0-A

D0-D

A0-A

19

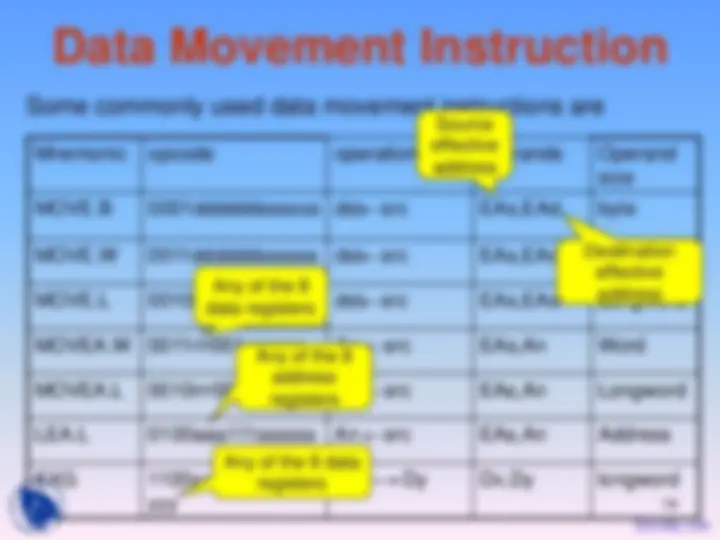

Source effective address

Destination effective Any of the 8 address data registers

Any of the 8 data registers

Any of the 8 address registers

20

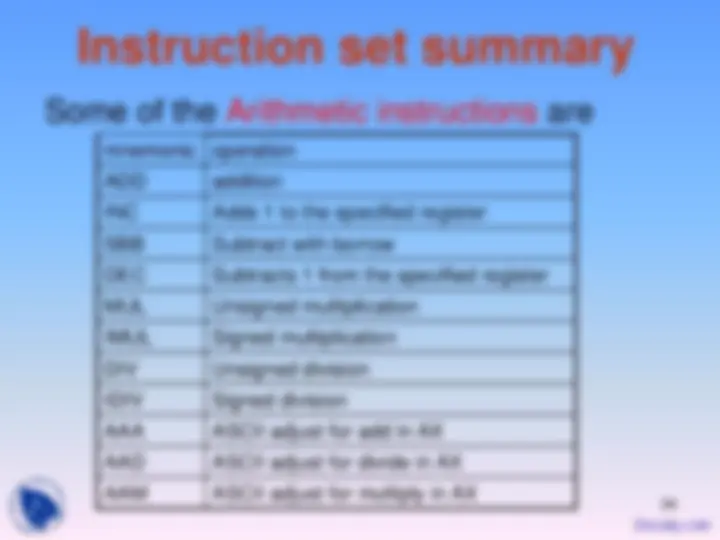

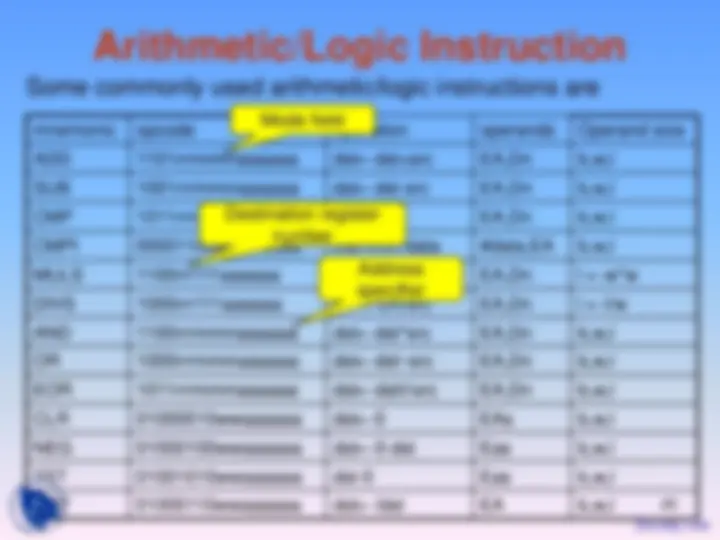

Arithmetic/Logic Instruction

mnemonic opcode operation operands Operand size ADD 1101rrrmmmaaaaaa dst←dst+src EA,Dn b,w,l SUB 1001rrrmmmaaaaaa dst←dst-src EA,Dn b,w,l CMP 1011rrrmmmaaaaaa Dst-src EA,Dn b,w,l CMPI 00001100wwaaaaaa Dst-imm data #data,EA b,w,l MULS 1100rrr111aaaaaa Dn ←Dnsrc EA,Dn l ←ww DIVS 1000rrr111aaaaaa Dn ←Dn/src EA,Dn l ←l/w AND 1100rrrmmmaaaaaa dst←dst^src EA,Dn b,w,l OR 1000rrrmmmaaaaaa dst←dst~src EA,Dn b,w,l EOR 1011rrrmmmaaaaaa dst←dst⊗src EA,Dn b,w,l CLR 01000010wwaaaaaa dst← 0 EAs b,w,l NEG 01000100wwaaaaaa dst←0-dst Eas b,w,l TST 01001010wwaaaaaa dst-0 Eas b,w,l NOT 01000110wwaaaaaa dst←!dst EA b,w,l

Mode field

Destination register number

Address specifier