Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

These are the Lecture Slides of Embedded System Design which includes Hardware Design, Elevator Controller, Simple Elevator Controller, Try Capturing, Unit Control, Request Resolver, Sequential Program Model, Partial English Description, System Interface etc. Key important points are: Pulse Width Modulator, Generates Pulses, Duty Cycle, Common Use, Control Average Voltage, Digital Analog Converter, Dimmer Lights, Encode Commands, Decode, Controlling

Typology: Slides

1 / 3

This page cannot be seen from the preview

Don't miss anything!

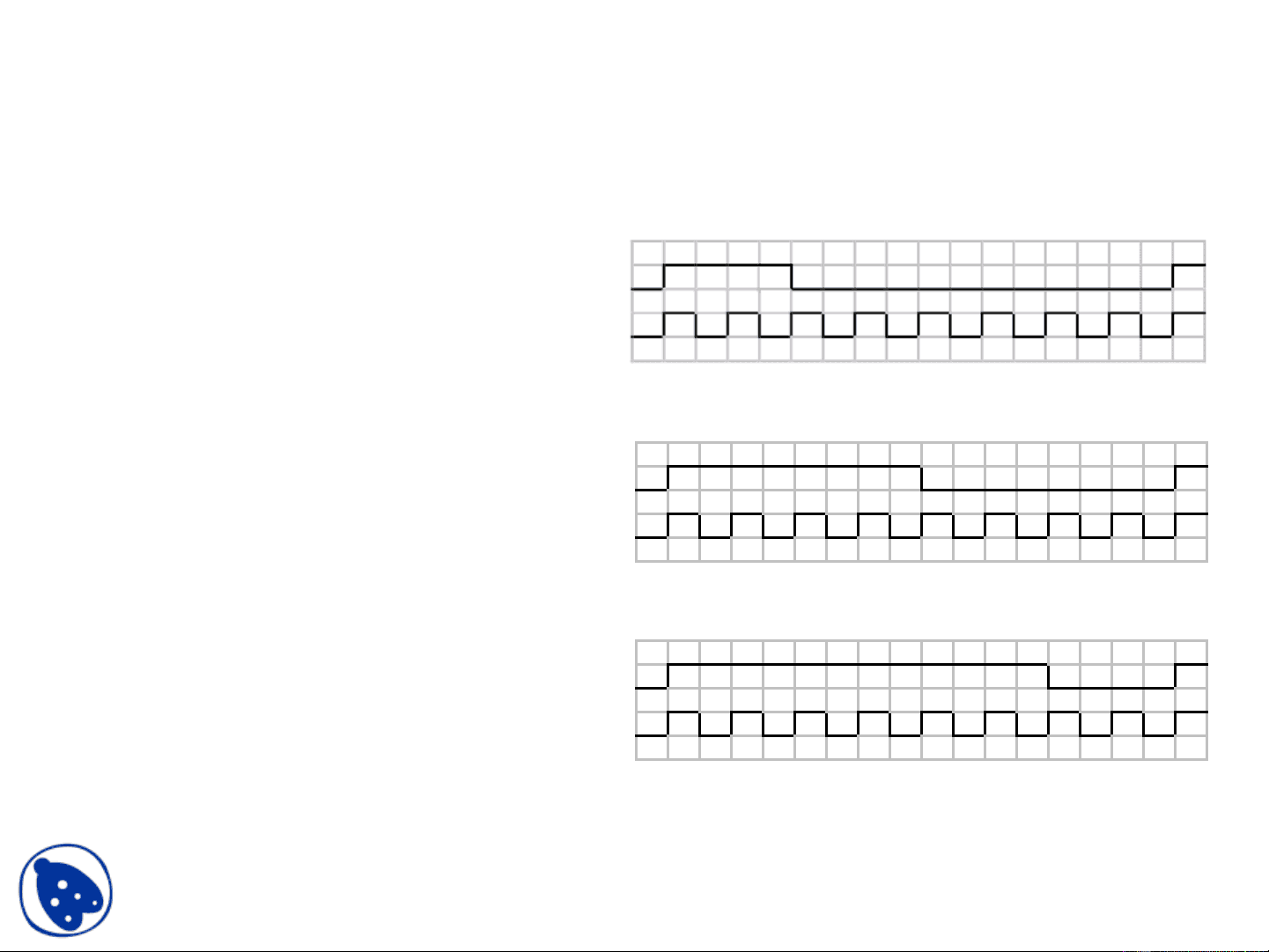

Controlling a DC motor with a PWM

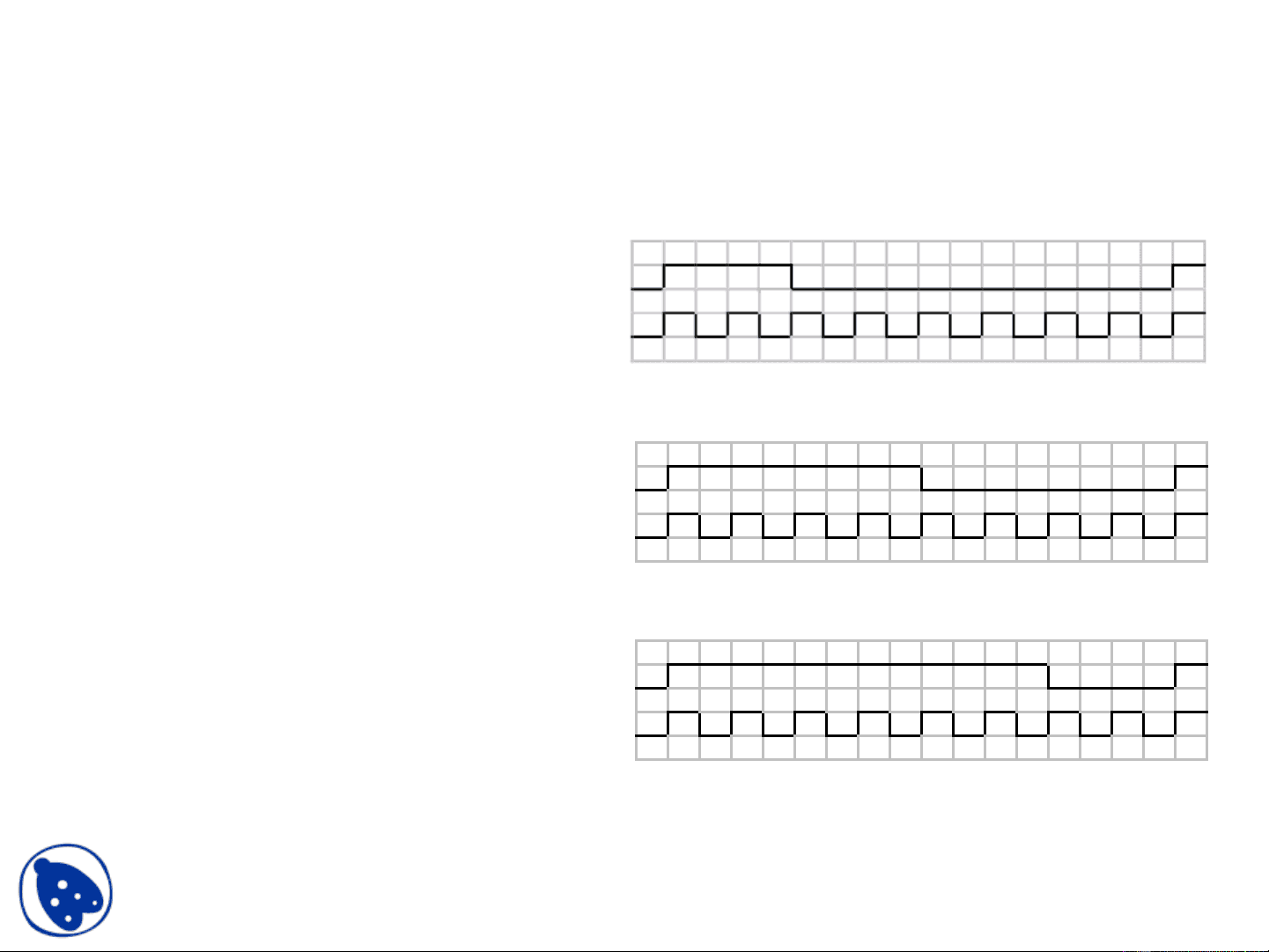

Internal Structure of PWM

clk_div

cycle_high

counter ( 0 – 254)

8-bit comparator

controls how fast the counter increments counter < cycle_high, pwm_o = 1 counter >= cycle_high, pwm_o = 0

pwm_o

clk Input Voltage^

% of Maximum Voltage Applied RPM of DC Motor

0 0 0

2.5 50 1840

3.75 75 6900

5.0 100 9200

Relationship between applied voltage and speed of the DC Motor