Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

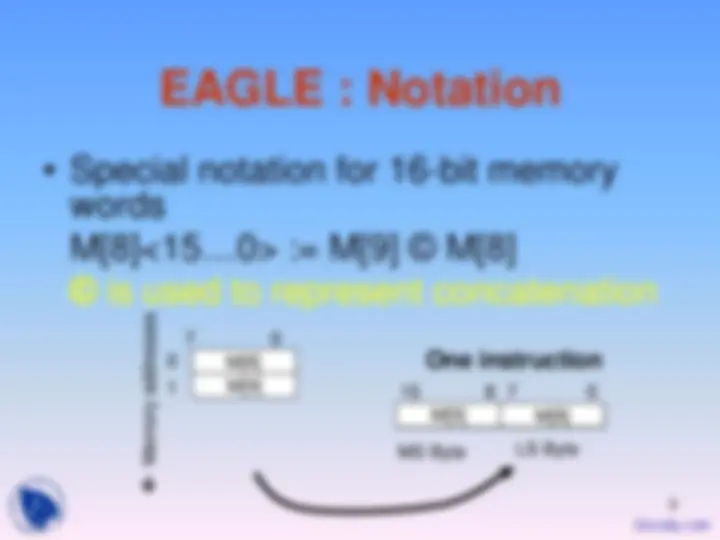

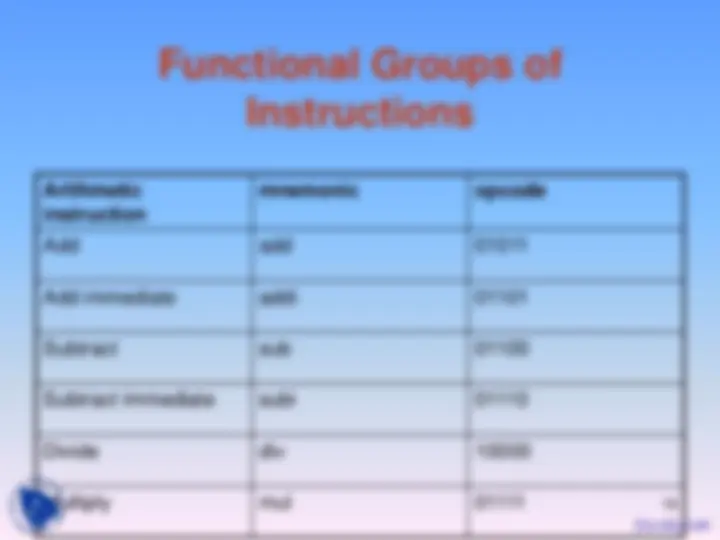

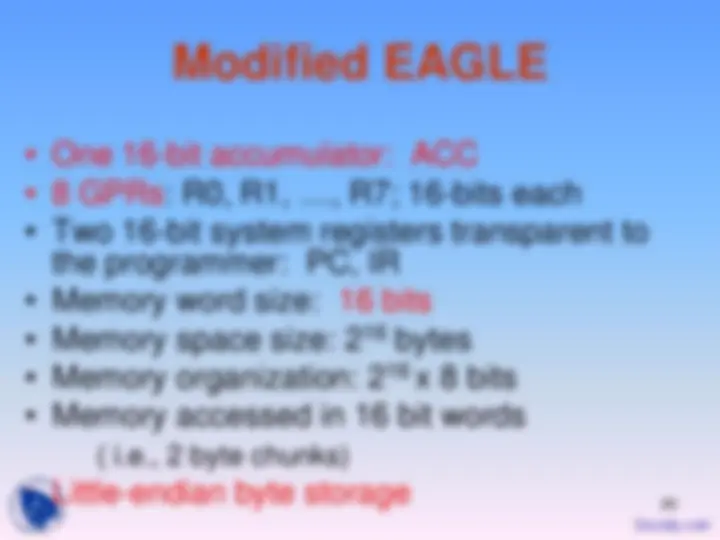

Programmer View of the EAGLE, Main memory, CPU, Notation, Instruction formats, Encoding for the GPRs, Data Transfer Instruction are the topics professor discussed in class.

Typology: Slides

1 / 21

This page cannot be seen from the preview

Don't miss anything!

1

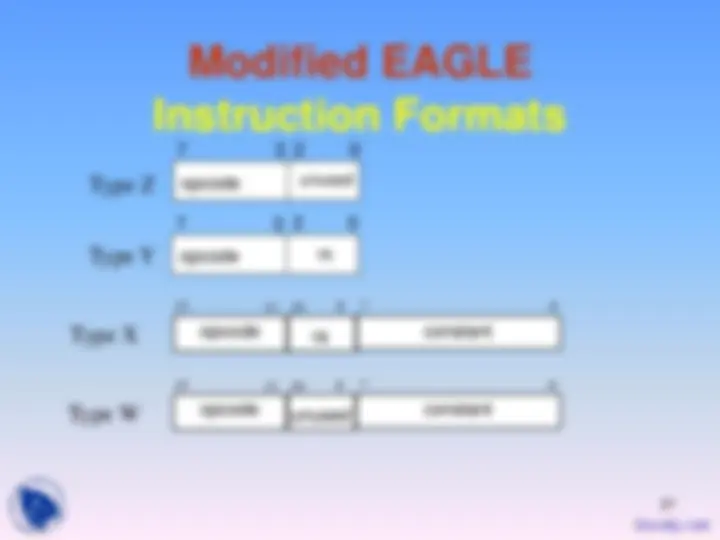

15 0 R R

R Register file

IR PC

2

4

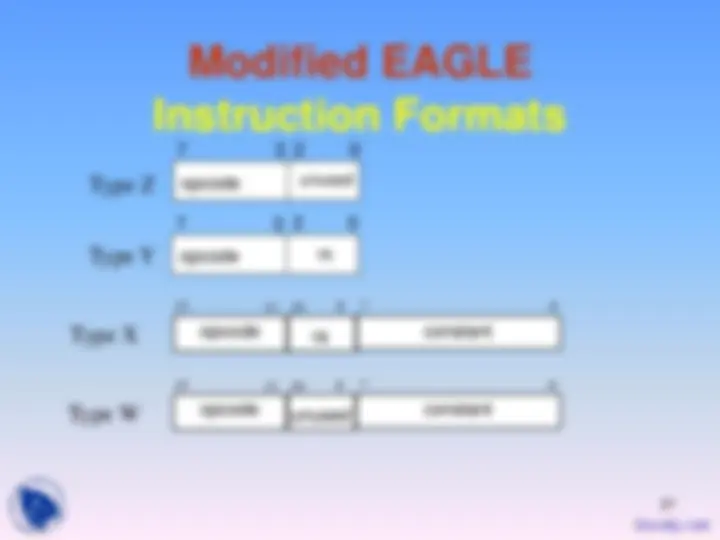

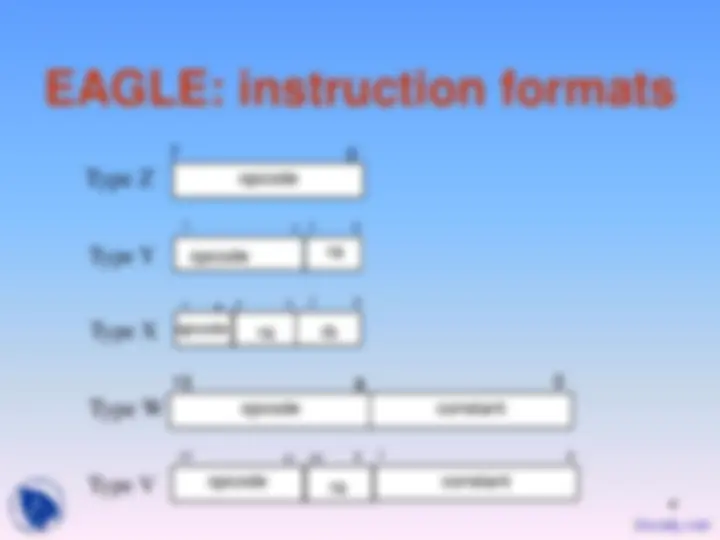

opcode

(^7 ) ra

0 Type Y

Type W opcode

(^158) constant

0

15 11 10 8 constant

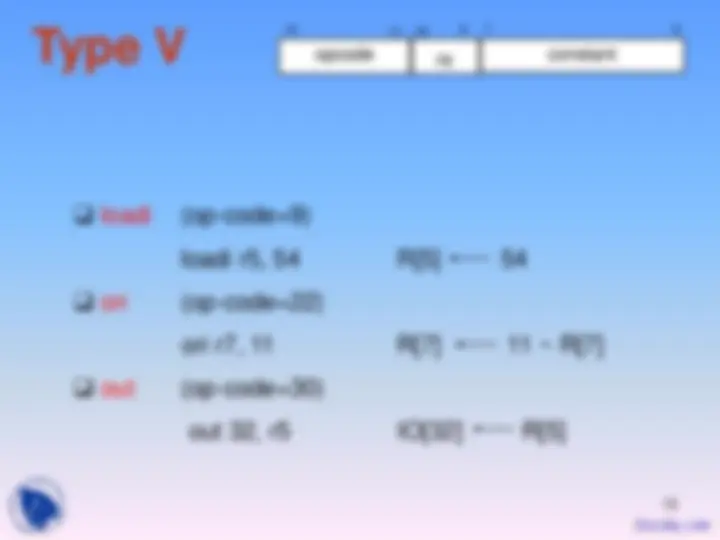

7 0 Type V opcode^ ra

7 6 ra

5 3 rb

2 0 Type X opcode^ ra rb

Type Z^ opcode

(^70)

2

5

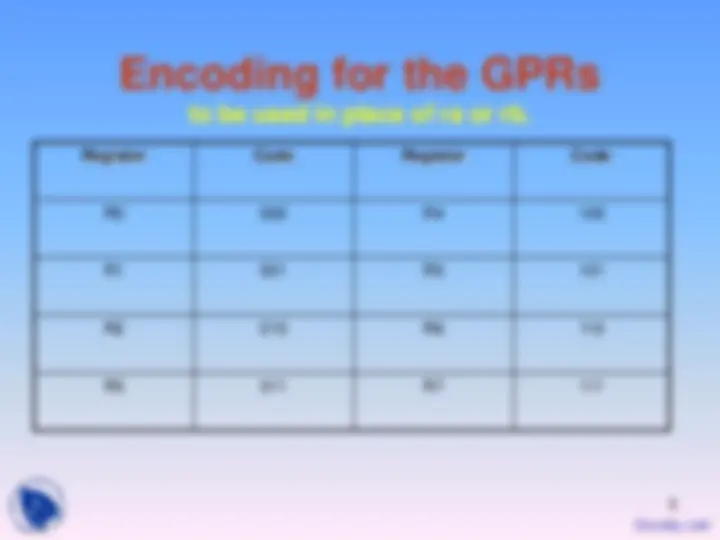

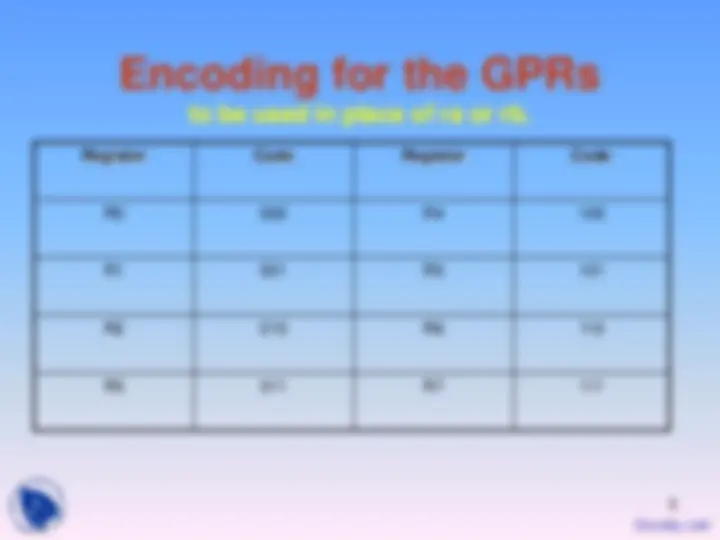

Encoding for the GPRs to be used in place of ra or rb.

Register Code Register Code

R0 000 R4 100

R1 001 R5 101

R2 010 R6 110

R3 011 R7 111

7

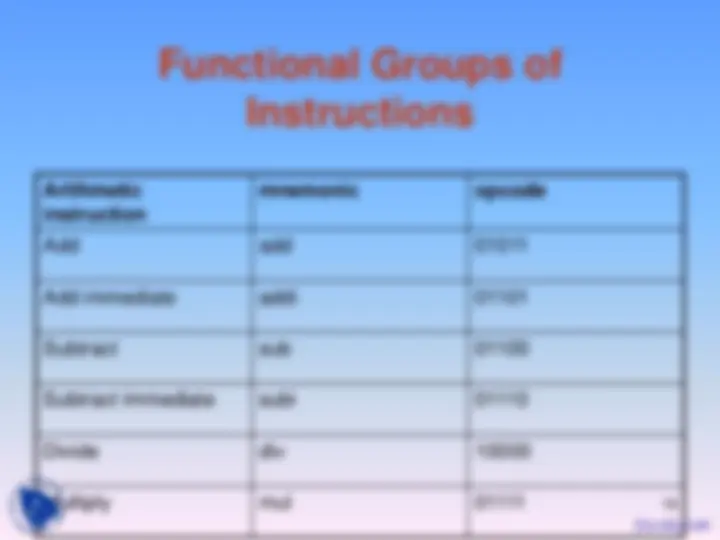

add (op-code = 11) add r1 R[0] R[1] + R[0]

and (op-code = 19) and r5 R[0] R[1] & R[0] div (op-code = 16)

div r6 R[0] R[0] / R[6] R[6] R[0] % R[6] mul (op-code = 15) mul r4 R[0] R[0] * R[4]

(^7 ) ra

0

8

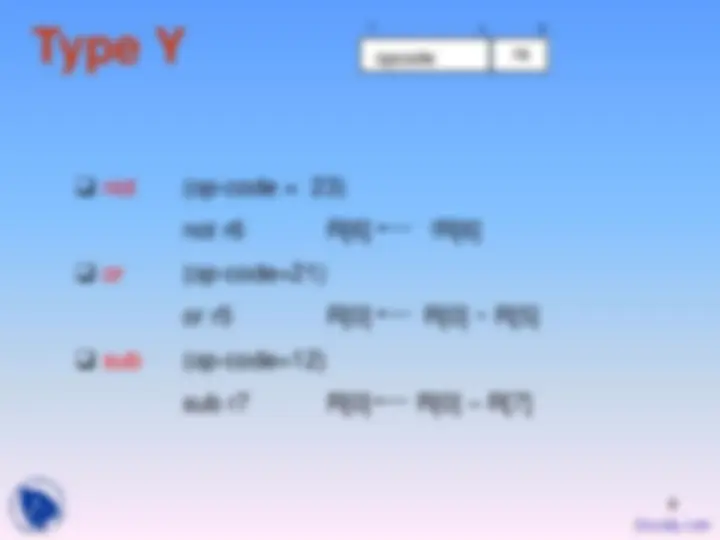

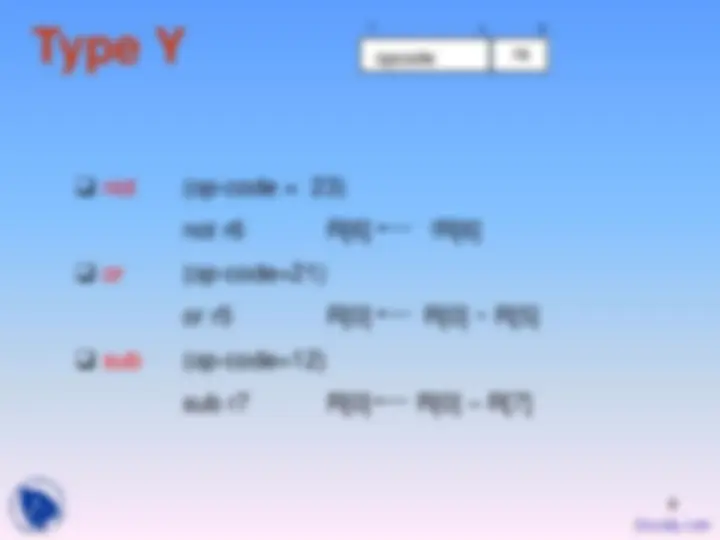

not (op-code = 23) not r6 R[6] !R[6] or (op-code=21) or r5 R[0] R[0] ~ R[5]

sub (op-code=12) sub r7 R[0] R[0] – R[7]

opcode

(^7 ) ra

0

10

opcode

(^158) constant

0

11

addi (op-code = 13) addi r4, 31 R[4] R[4] +

andi (op-code = 20 ) andi r6, 1 R[6] R[6] & in (op-code=29) in r1, 45 R[1] IO[45] load (op-code=8)

load r3, 6 R[3] M[6]

15 11 10 8 constant

7 0 opcode (^) ra

13

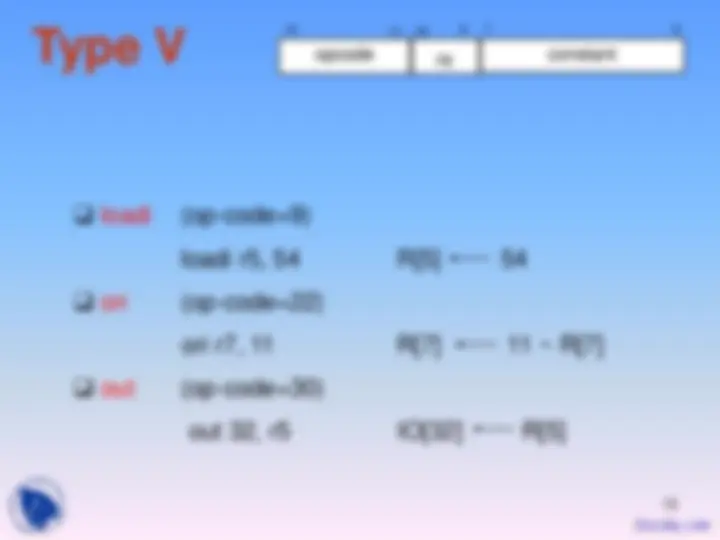

loadi (op-code=9)

loadi r5, 54 R[5] 54 ori (op-code=22) ori r7, 11 R[7] 11 ~ R[7] out (op-code=30) out 32, r5 IO[32] R[5]

15 11 10 8 constant

7 0 opcode (^) ra

14

shiftl (op-code=17)

shiftr( op-code=18)

store (op-code=10)

subi (op-code=14)

15 11 10 8 constant

7 0 opcode (^) ra

16

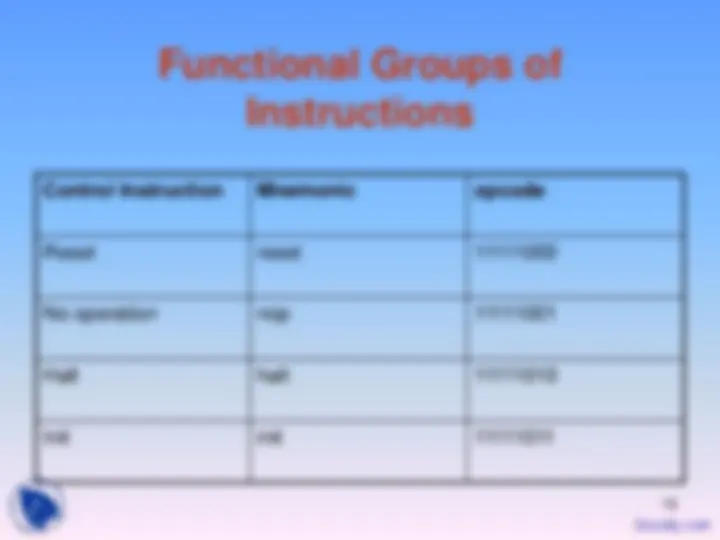

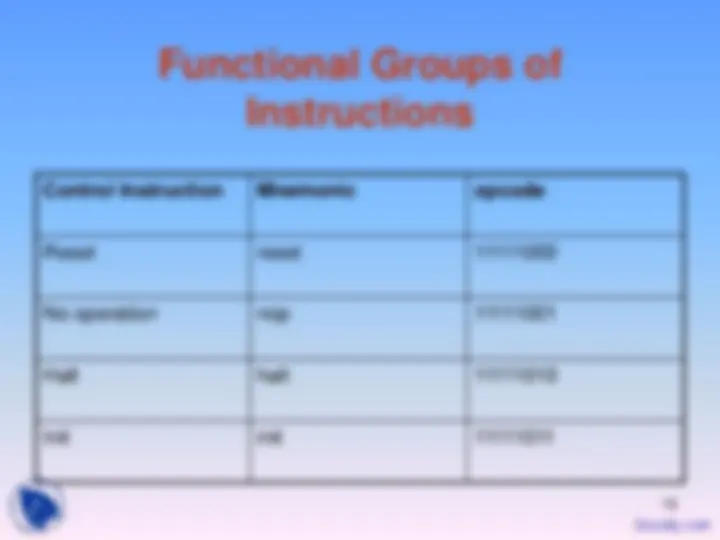

Data Transfer Instruction

mnemonic opcode

Input in 11101

Output out 11110

Move mov 00

Load from memory load 01000

Load constant loadi 01001

Store into memory store 01010

17

Branch if negative brn 11100

Branch if not zero brnz 11001

Branch if zero brz 11010

Branch if positive brp 11011

Branch br 11111100

19

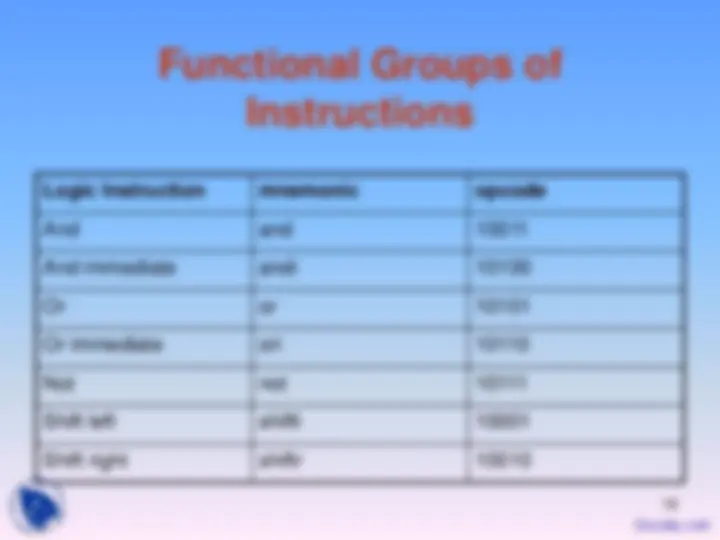

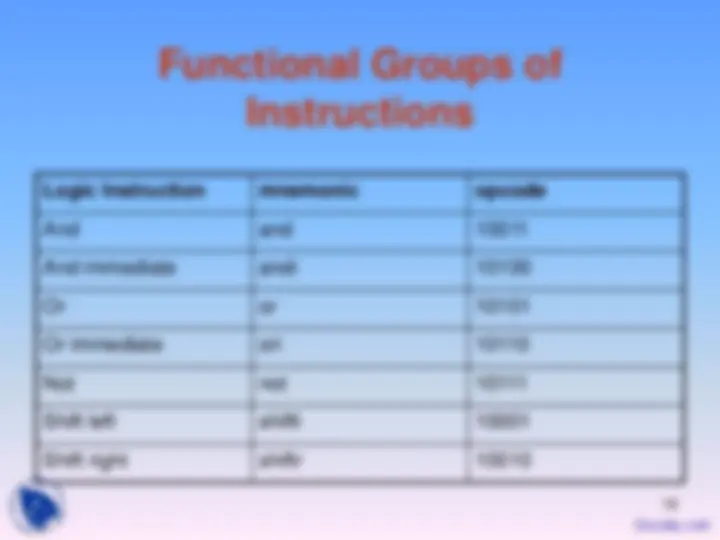

Logic Instruction mnemonic opcode

And and 10011

And immediate andi 10100

Or or 10101

Or immediate ori 10110

Not not 10111

Shift left shiftl 10001

Shift right shiftr 10010

20