Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

Processor State, RTL, Dynamic Properties, FALCON A, Effective Address Calculations, Relative Address, Range of Memory Addresses are the topics professor discussed in class.

Typology: Slides

1 / 31

This page cannot be seen from the preview

Don't miss anything!

1

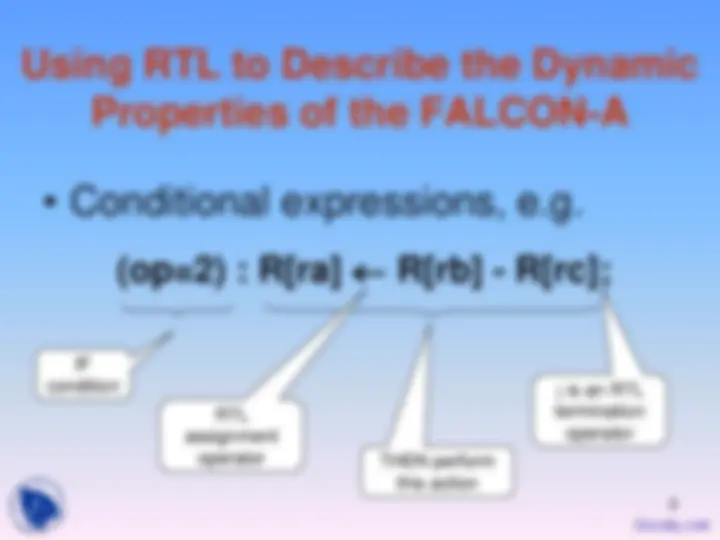

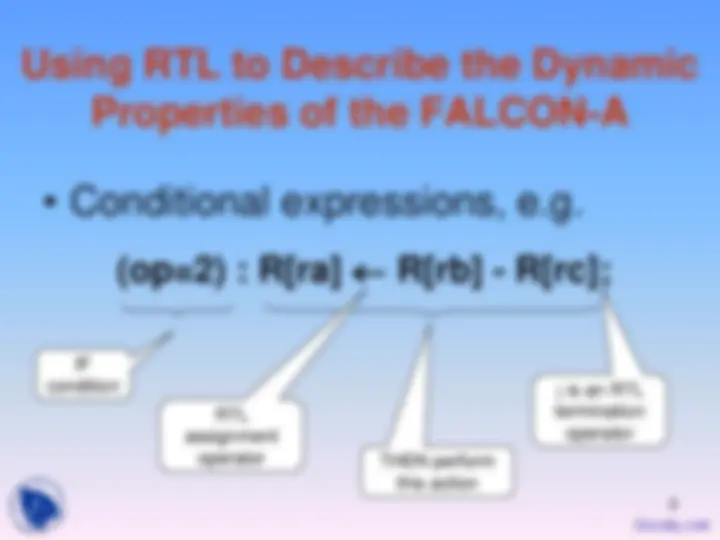

RTL naming operator

2

Describing the Processor

State Using RTL

4

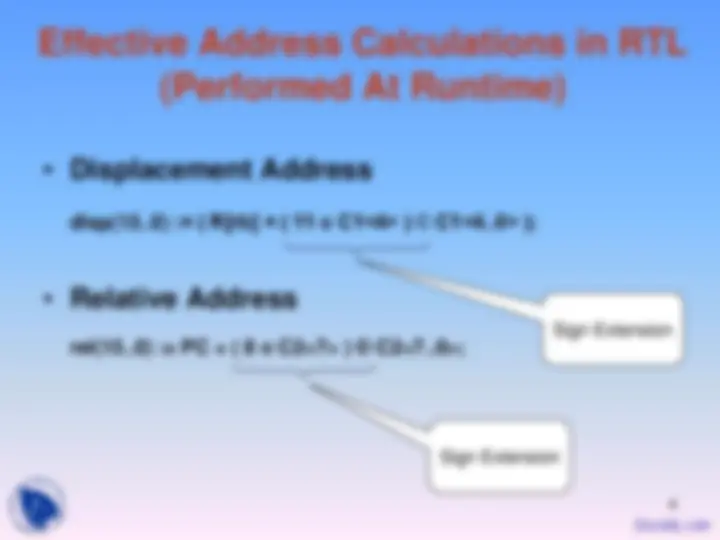

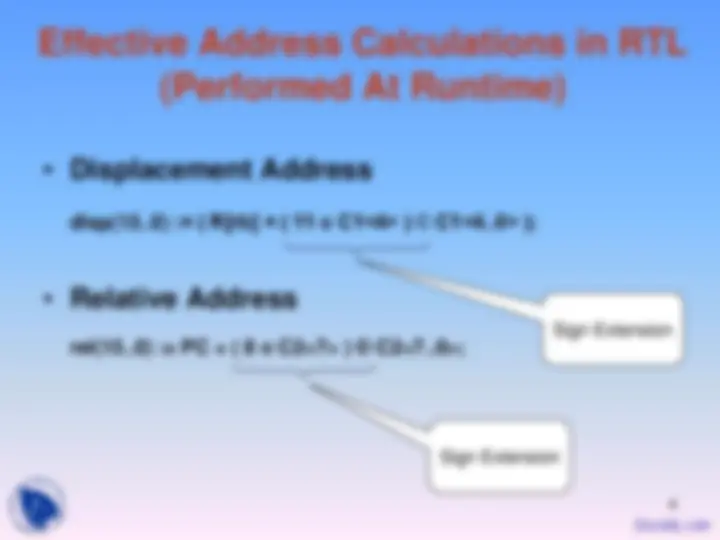

Effective Address Calculations in RTL

(Performed At Runtime)

disp〈15..0〉 := ( R[rb] + ( 11 α C1<4> ) © C1<4..0> );

rel〈15..0〉 := PC + ( 8 α C2<7> ) © C2<7..0>;

Sign Extension

Sign Extension

5

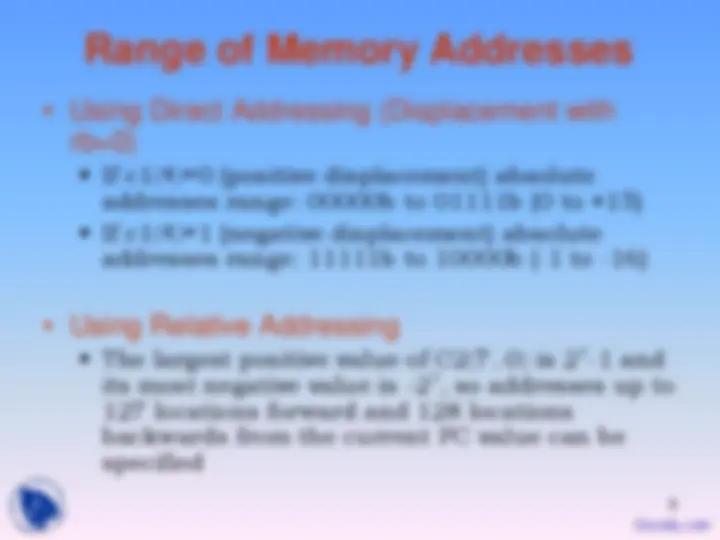

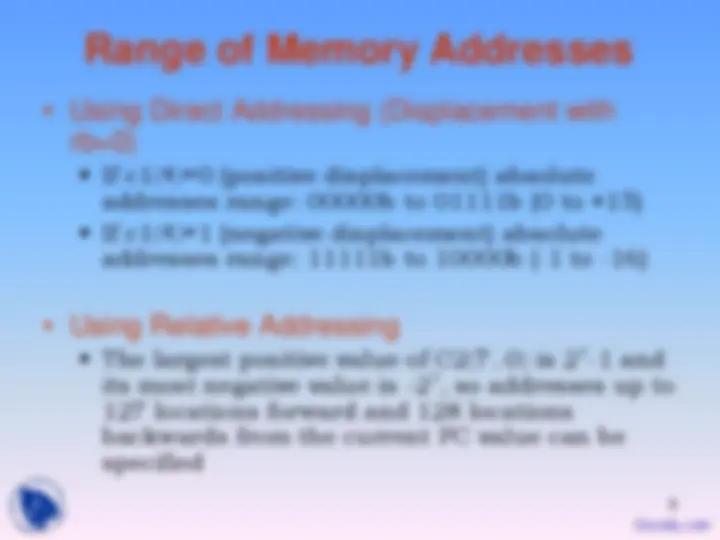

If c1〈 4 〉=0 (positive displacement) absolute addresses range: 00000b to 01111b (0 to +15) If c1〈 4 〉=1 (negative displacement) absolute addresses range: 11111b to 10000b (-1 to -16)

The largest positive value of C2〈7..0〉 is 2 7 -1 and its most negative value is -2 7 , so addresses up to 127 locations forward and 128 locations backwards from the current PC value can be specified

7

Instruction Fetch

Instruction Decode

Op-code = 0

Op-code = 30 Op-code = 1

appropriate processing goes in this place

8

(Jump Instructions)

... ... (op<4..0> = 20) : ( cond : PC ← R[ra] + c2(sign extended) ), unconditional branch (jump) (op<4..0> = 16) : cond : ( PC ← PC + C2(sign extended) ), conditional jump (jpl) ... ...

10

(Shift Instructions)

... ...

(op<4..0>=12) : R[ra]〈15..0 〉 ← R[rb]<( 15 – N )..0> © ( N α 0 ); (op<4..0>=13) : R[ra]〈15..0 〉 ← ( N α 0 ) © R[rb]<15..N>; (op<4..0>=15) : R[ra]〈15..0 〉 ← N α ( R[rb]<15> ) © ( R[rb]<15..N> );

... ...

Notation: α means replication © means concatenation

Shift

Shift Right

Left

Arithmetic Shift Right

11

(Data Transfer Instructions)

... ...

(op<4..0>=29) : R[ra] ← M[R[rb] + (11 α C1<4>) © C1<4..0>];

(op<4..0>=28) : M[R[rb] + (11 α C1<4>) © C1<4..0>] ← R[ra];

(op<4..0>=6) : R[ra] ← R[rb];

(op<4..0>=7) : R[ra] ← (8 α C2<7>) © C2<7..0>;

(op<4..0>=24) : R[ra] ← IO[c2];

(op<4..0>=25) : IO[c2] ← R[ra];

... ...

load store mov movi

in

out

13

14

16

17

19

20