Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

An in-depth exploration of sop (sum of products) and pos (product of sums) forms in digital logic. It covers notation, computation methods, canonical forms, and examples using truth tables and boolean functions. The document also discusses the advantages and applications of both sop and pos forms.

Typology: Slides

1 / 28

This page cannot be seen from the preview

Don't miss anything!

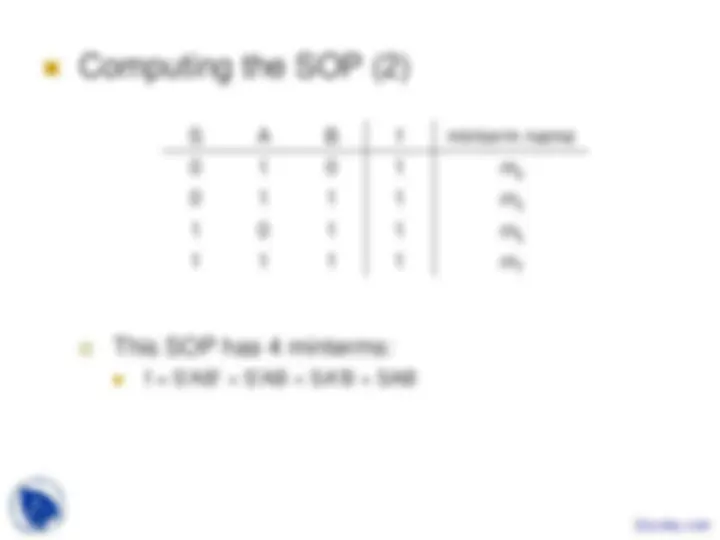

S A B f 0 0 0 0 0 0 1 0 0 1 0 1 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 0 1 1 1 1

f = S'AB' + S'AB + SA'B + SAB

or

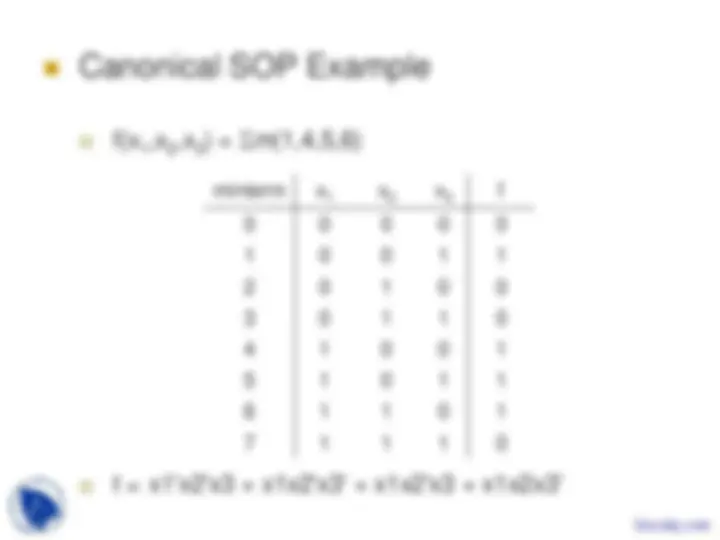

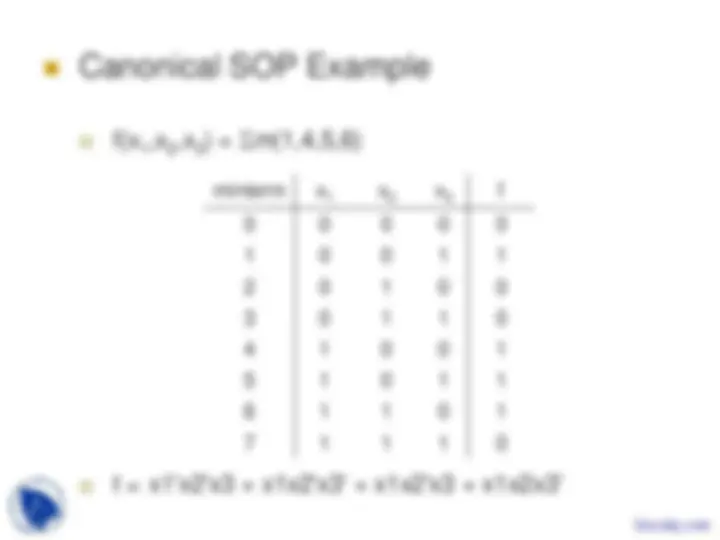

minterm x 1 x 2 x 3 f 0 0 0 0 0 1 0 0 1 1 2 0 1 0 0 3 0 1 1 0 4 1 0 0 1 5 1 0 1 1 6 1 1 0 1 7 1 1 1 0

A logical “sum” of the input bits which guarantees that term will be “0” (sum of literals) A B f 0 0 0 0 1 1 1 0 0 1 1 0

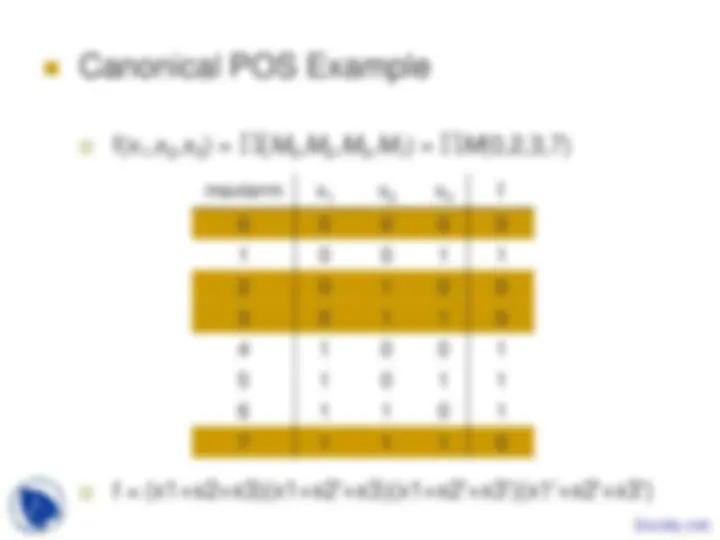

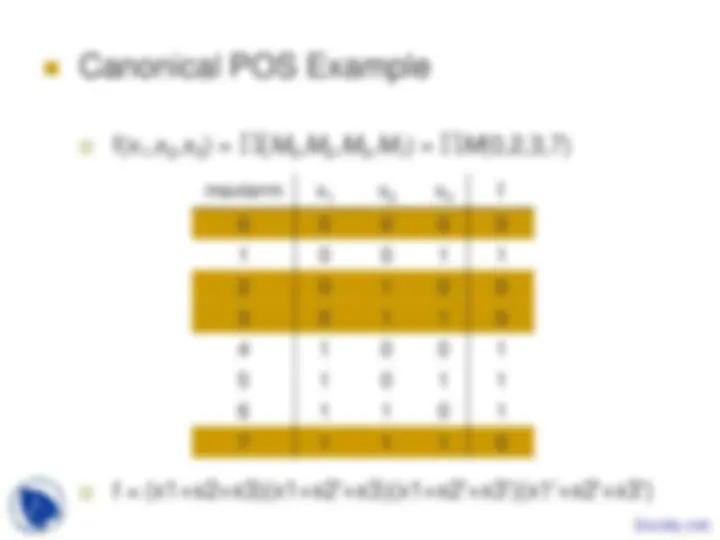

f(x 1 ,x 2 ,x 3 ) = ( M 0 , M 2 , M 3 , M 7 ) = M (0,2,3,7)

maxterm x 1 x 2 x 3 f 0 0 0 0 0 1 0 0 1 1 2 0 1 0 0 3 0 1 1 0 4 1 0 0 1 5 1 0 1 1 6 1 1 0 1 7 1 1 1 0

Under what conditions would POS form be better?

This is why we do not always count them among the cost of a circuit

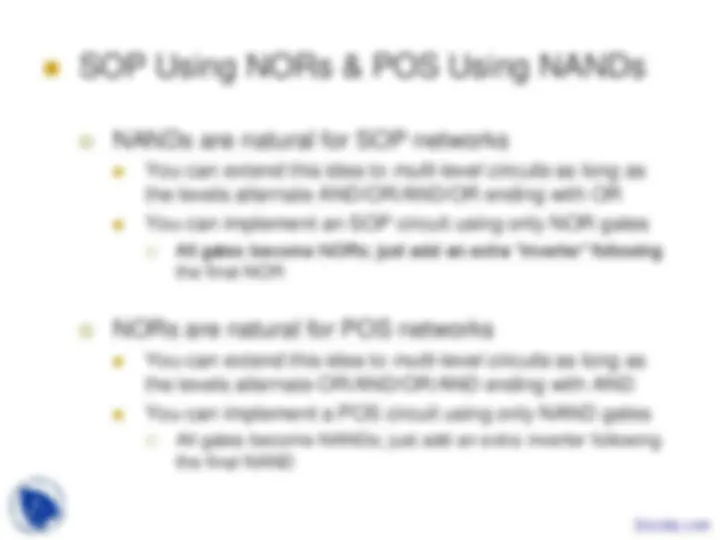

Any Boolean function can be implemented

using just NAND gates. Why?

Likewise for NOR

“pushing the bubbles” Every gate just becomes a NAND!

x 1 x 2 x 3 x 4 x 5

x 1 x 2 x 3 x 4 x 5

x 1 x 2 x 3 x 4 x 5

NAND and NOR require fewer transistors to build Just having a single gate design is simpler than having 3!