Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

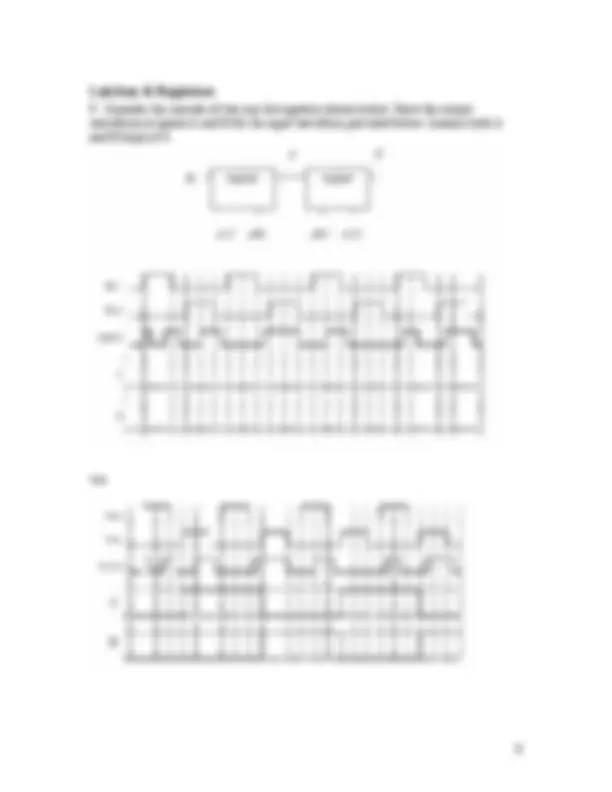

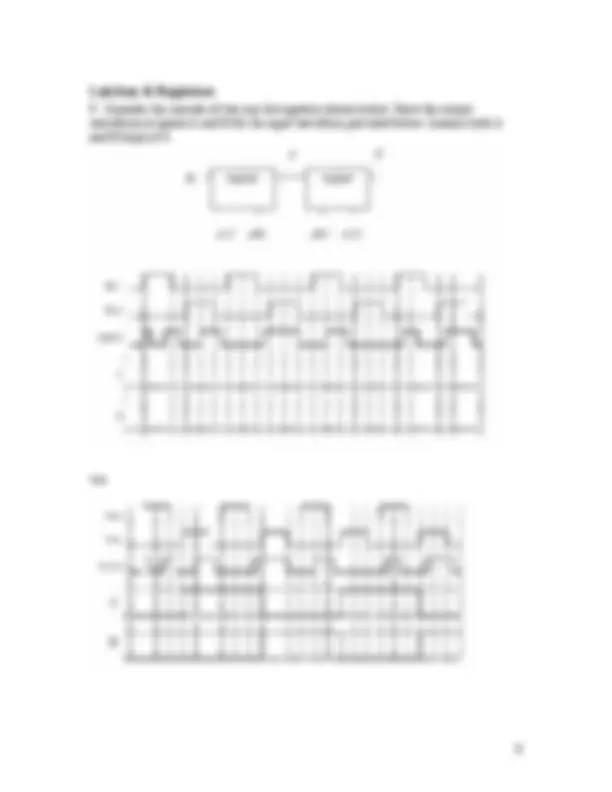

Main points of this past exam are: Network Connecting, Network Connecting, Control Signal, Signed Operations, Complement Numbers, Subtractor, Multiplexors,, Basic Gates, One-Bit Registers, Truth Table

Typology: Exams

1 / 9

This page cannot be seen from the preview

Don't miss anything!

A B Ci S Co 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1

(1100.0011) 2 = 14.14 (^8) (178) 16 = 1(16) 2 + 7(16) + 8(1) = 376 10 (46.5625) 10 = 101110.1001 (^2)

b. Convert 46.25 to IEEE 754 single precision format and provide the hexadecimal value of the encoding.

First convert 46.25 to binary = 101110. Since the number is +ve sign bit is 0. Rewriting the number 1.0111001 x 2^5. Expanding the fraction to 23 bits 01110010000000000000000. The exponent is 5. Biasing 5 + 127 = 132. In binary this is 10000100. Putting this all together 01000010001110010000000000000000 0x

Two’s Complement -2 n-1^2 n-1^ - 1

Sign Magnitude -2n-1^ - 1 2 n-1^ - 1

Ans