Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

This document from docsity.com provides an in-depth explanation of the different types of semiconductor memory, including static ram (sram), dynamic ram (dram), and read only memory (rom). It covers the structure, operation, and advantages/disadvantages of each type, as well as details on refreshing, packaging, organization, error correction, and synchronous dram. Additionally, it introduces rambus as a main competitor to sdram.

Typology: Slides

1 / 29

This page cannot be seen from the preview

Don't miss anything!

Chapter 5

Internal Memory

Semiconductor Memory Types

Memory Cell Operation

Dynamic RAM

DRAM Operation

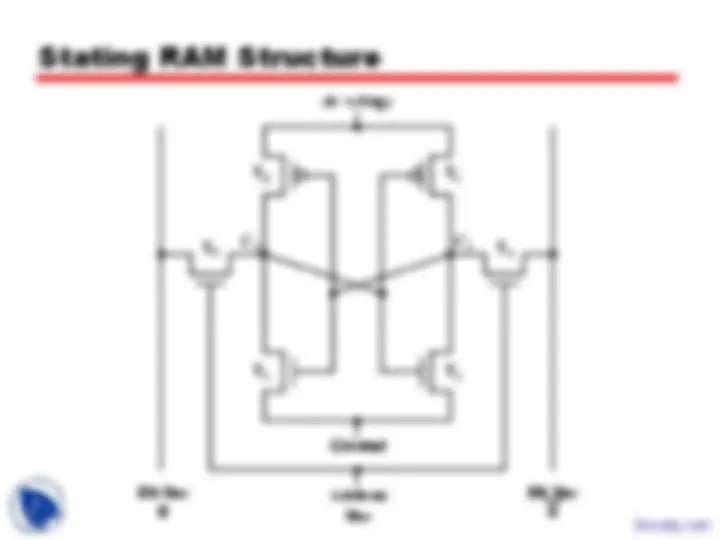

Static RAM

Static RAM Operation

SRAM v DRAM

Types of ROM

Organisation in detail

Typical 16 Mb DRAM (4M x 4)

Packaging

1M X 8 bit 4M X 4 bit

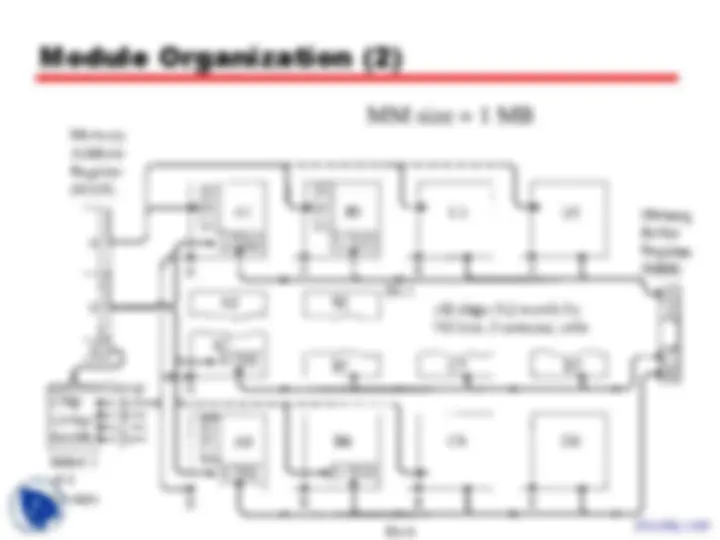

Module Organization (2)

MM size = 1 MB

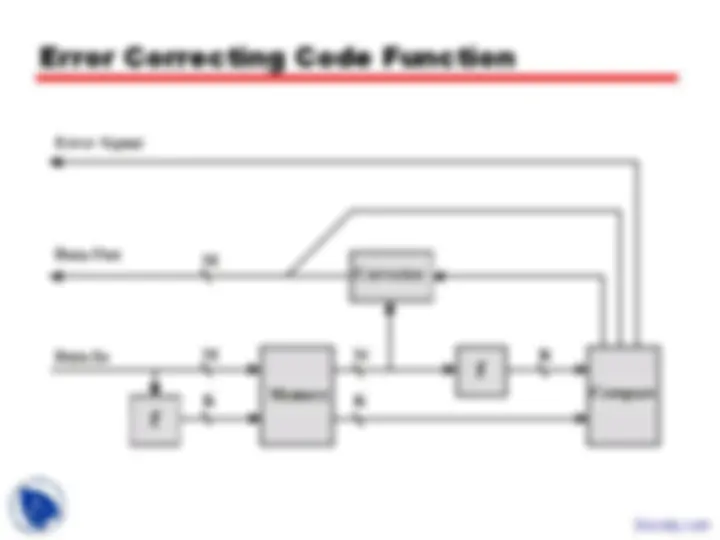

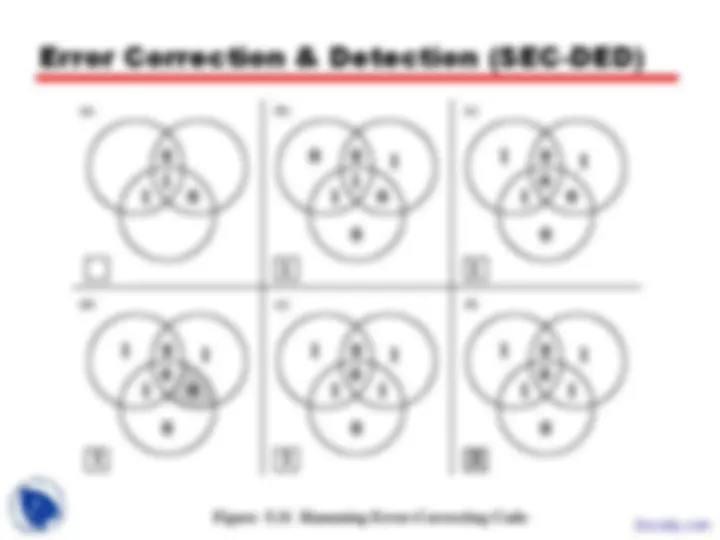

Error Correction